Vivado数字逻辑电路设计入门教程

需积分: 31 184 浏览量

更新于2024-07-21

1

收藏 2.14MB PDF 举报

"Vivado使用简介 - 南京大学数字电路课程讲义,由名师编写,涵盖了Vivado的基本使用流程,包括创建模块、用户约束文件、建立Vivado工程、模块插入、约束声明、仿真、综合、设计实现、位文件生成及硬件下载等步骤。"

在数字电路设计领域,Vivado是一款由Xilinx公司推出的集成开发环境,主要用于FPGA(Field-Programmable Gate Array)的设计和实现。Vivado提供了完整的工具链,支持从高层次的系统级设计到门级的详细设计,再到硬件的验证和部署。

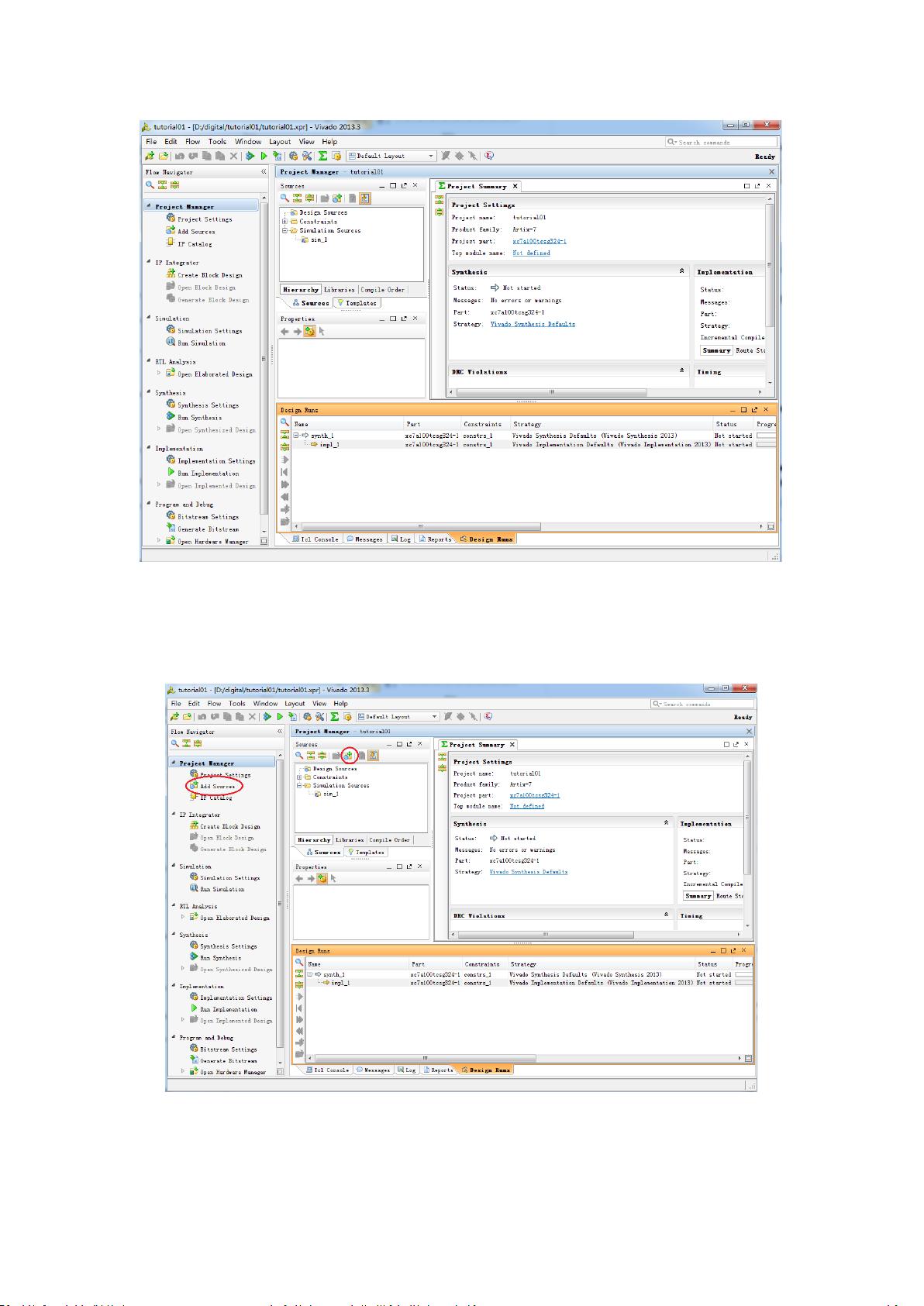

**创建Vivado工程**

1. **启动Vivado**: 通过启动菜单或者桌面快捷方式打开Vivado软件。首次使用时,可以选择"CreatingNewProject"来创建一个新的工程。

2. **设置工程属性**: 在新建工程向导中,指定工程的名称和位置。建议在一个专门的文件夹下创建所有课程相关的项目,并确保工程名称和路径不含中文字符或空格,可采用字母、数字和下划线组合。

3. **选择工程类型**: 选择"RTLProject",表示我们将进行寄存器传输级(Register Transfer Level)的设计,不立即添加源文件,即勾选"Donotspecifysourcesatthistime"。

4. **选定目标器件**: 根据实验板选择相应的FPGA型号。例如,Nexys4开发板使用的是Artix系列的FPGA。

**设计流程**

1. **创建模块**: 在Vivado中编写Verilog或VHDL代码,定义电路的逻辑功能,这些代码文件就是设计的模块。

2. **用户约束文件**: 创建用户约束文件(UCF或XDC),用于定义时钟、引脚分配等硬件限制。

3. **插入模块**: 将设计的模块添加到工程中,这些模块将成为设计的核心部分。

4. **声明约束**: 在工程中声明并应用约束文件,确保硬件资源的正确分配。

5. **仿真**: 使用Vivado内置的仿真工具对设计进行行为级验证,确保逻辑设计满足预期功能。

6. **综合**: 综合是将高级语言描述的逻辑转换成门级网表的过程,Vivado会优化设计以提高性能和资源利用率。

7. **实现设计**: 设计实现阶段,Vivado会根据综合后的网表布局布线,生成硬件配置文件。

8. **生成位文件**: 最终的位流文件(bitstream)包含了配置FPGA所需的所有信息。

9. **下载验证**: 通过JTAG或SPI接口将位文件下载到FPGA硬件中,进行实际电路的验证。

**注意事项**

- 在整个设计过程中,应定期进行检查和验证,确保每个步骤都符合设计需求。

- 设计完成后,需要考虑功耗、速度和面积等因素,对设计进行优化。

- 实际下载硬件之前,一定要确保仿真结果正确无误,避免硬件损坏。

以上内容详细介绍了Vivado的基本使用方法和一个典型的设计流程,对于初学者来说,理解并熟练掌握这些步骤是进行FPGA设计的基础。在学习过程中,结合南京大学的数字电路课程讲义和Vivado的官方文档,将有助于更深入地理解和应用这个强大的工具。

130 浏览量

549 浏览量

2036 浏览量

192 浏览量

116 浏览量

157 浏览量

245 浏览量

1436 浏览量

AlbertClock

- 粉丝: 0

- 资源: 1

最新资源

- 自动抄表系统中几种传感器的应用

- Vxworks入门实验

- Spring框架的简要分析.doc

- Operating System(Chapter 1)

- RDP协议详解(remote desktop protocol)

- Resin_brochure

- eclipse中文文档

- ASP.NET 不仅仅是 Active Server Page (ASP) 的下一个版本;它还提供了一个

- C#和.Net的优点研究了一下C#和.Net,有很多体会,好的不好的都有。随便谈谈,供大家参考。

- 深入理解计算机系统(英文版)

- Practical UML Statecharts in C,C++, Second Edition.pdf

- JSP 实用教程 (第二版) 代码

- 经典c程序编程100例

- 常用DIV+CSS网页制作布局技术技巧

- scilab 软件的帮助说明

- PowerPCB教程.pdf