使用VHDL在FPGA上实现的电子钟设计与仿真

版权申诉

111 浏览量

更新于2024-07-04

收藏 1.45MB DOC 举报

"基于FPGA的电子钟设计文档详细介绍了如何使用VHDL语言设计一个电子钟,并通过FPGA实现。文档涵盖了VHDL的基本语法、FPGA技术介绍、系统设计方案以及程序设计的各个模块,包括时钟分频、计时、按键处理和显示等关键部分。"

本文档详细阐述了一项基于FPGA的电子钟设计项目,利用VHDL这一硬件描述语言进行开发。VHDL具有强大的硬件描述能力,使得复杂的数字系统设计变得更为直观和便捷。文档首先对VHDL进行了简要介绍,强调了其在现代电子设计中的重要性,以及与传统电路设计的区别。

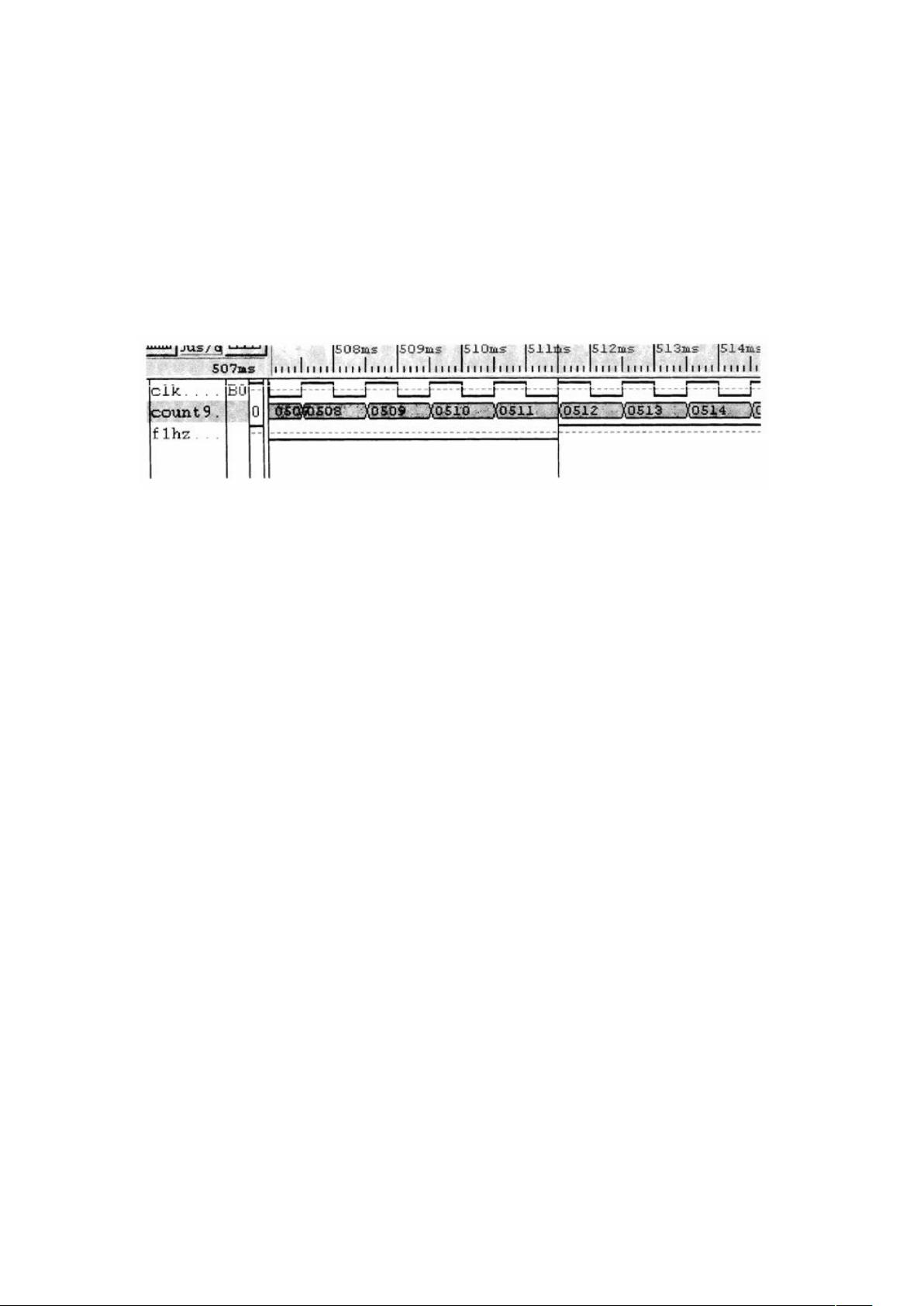

设计的电子钟包含四个主要部分:时钟分频模块用于生成精确的时钟信号;计时模块负责时间的计数和更新;按键模块处理用户输入,如设置闹钟或暂停计时;显示模块则将时间信息通过七段数码管呈现出来。文档详细列出了各部分的组件设计,如1Hz_generator用于生成1Hz时钟,count60和count24组件分别用于分钟和小时的计数,alarm_set组件处理闹钟设定,stop_watch组件可能用于暂停或恢复计时功能,i60bcd和i24bcd组件则将十进制时间转换为BCD(二进制编码的十进制)格式以驱动七段显示器。

系统模块设计部分,文档介绍了七段显示器的扫描输出电路、entity模块和architecture模块,这些都是实现电子钟显示和逻辑控制的核心。此外,还详细讲解了正常计数时间功能和扫描多路输出功能的实现方法,确保电子钟能够准确、稳定地显示时间。

在总结部分,作者提到这个项目的意义在于提高时间管理的便利性,特别是在快节奏的生活中。同时,设计和实现这样一个电子钟项目,也为学习者提供了深入理解和应用FPGA及VHDL语言的机会,有助于提升电子设计技能。

这份文档是一个全面的FPGA开发教程,适用于想要掌握VHDL语言和FPGA设计的学生或工程师。通过这个项目,读者不仅可以学习到VHDL的基本语法和设计流程,还能了解到FPGA在实际电子系统中的应用,从而提升自身的硬件设计能力。

118 浏览量

606 浏览量

2023-06-20 上传

162 浏览量

206 浏览量

2022-03-28 上传

251 浏览量

511 浏览量

3087 浏览量

zzzzl333

- 粉丝: 815

- 资源: 7万+

最新资源

- 送药小车毕业设计送药小车毕业设计

- sxiv-patches:一组用于sxiv图像查看器的补丁

- minikube-nfs-test:在minikube上安装NFS服务器客户端的各种资源

- FreeRiderHMC

- Box's Evolutionary algorithm:求解多变量无约束优化-matlab开发

- 动科(DK)企业网站管理系统 v9.2

- scheamer

- Karabiner-Elements-12.8.0.dmg.zip

- 校园志愿者活动管理系统-志愿者小程序(含管理后台)-毕业设计

- ditto-subgraph

- astlog:星号SIP日志解析器

- Addon-Bluetooth-WebGUI:适用于FABI和FLipMouse的ESP32插件,添加了蓝牙和WiFiWebGUI支持

- 模拟

- MP4

- unist-util-modify-children:修改父母直系子女的实用程序

- 信呼协同办公系统 v1.6.0