华为FPGA设计高级技巧:Xilinx篇—优化与资源利用

需积分: 9 118 浏览量

更新于2024-07-24

2

收藏 2.93MB PDF 举报

本资源是一份名为《华为_FPGA设计高级技巧Xilinx篇》的内部文档,由深圳市华为技术有限公司研究管理部文档中心编写,针对Xilinx FPGA设计提供高级技巧。文档共有62页,涵盖了多个关键主题,旨在帮助设计师优化设计效率和性能。

1. **逻辑设计策略**:

- **加法器设计**:介绍了如何通过合理选择加法电路(如串行进位与超前进位、使用圆括号处理多路加法)来减少关键路径的逻辑级数,提高设计速度。

- **条件语句**:讨论了IF语句和Case语句的使用,强调它们在控制流中的作用以及如何平衡速度和面积的关系。

2. **资源利用和性能提升**:

- **LUT配置**:解释了如何将LUT配置为组合逻辑电路,虽然门数增加,但逻辑级数保持不变,同时能减少资源占用,提高时序性能。

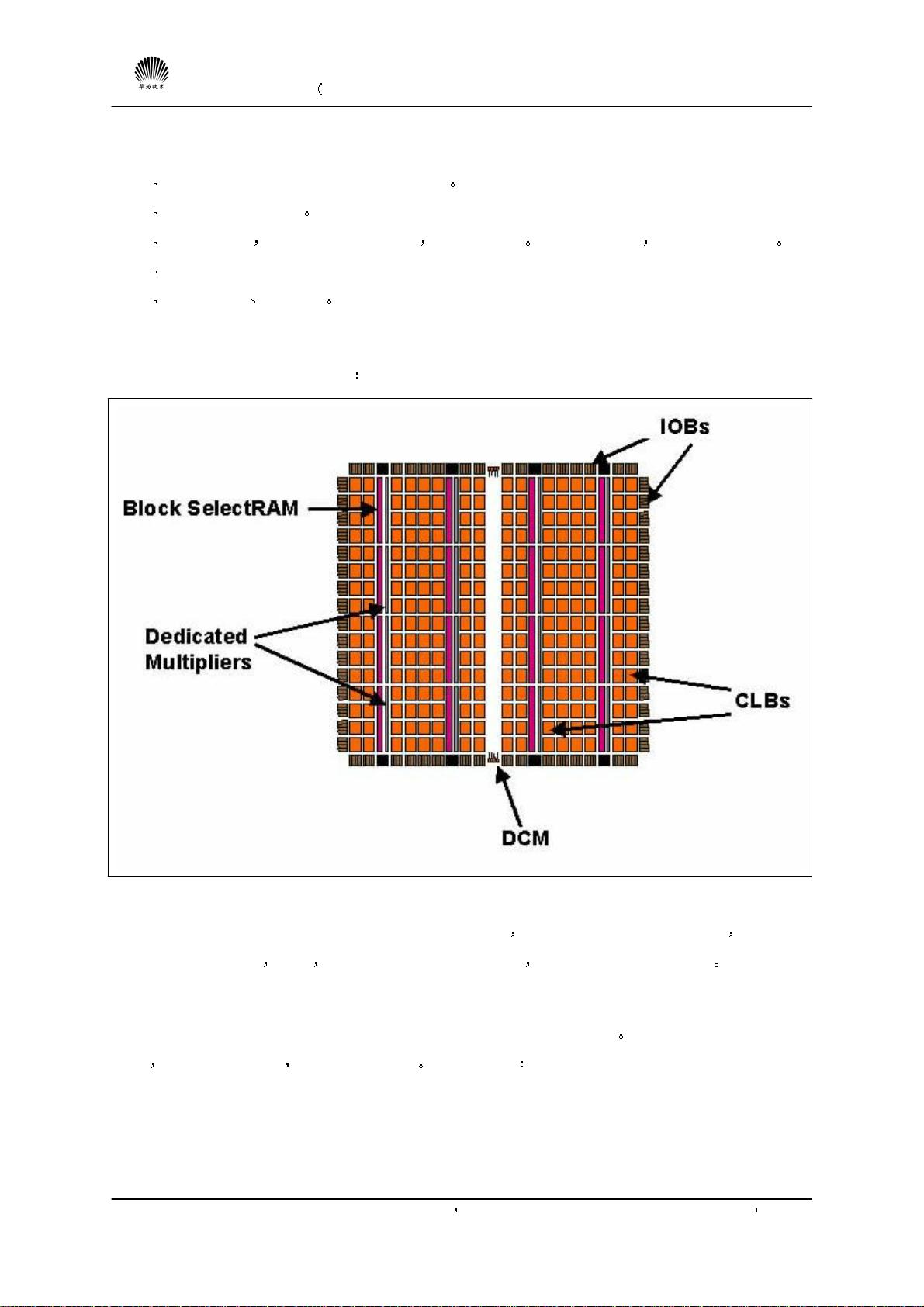

- **内存模块**:涉及BlockSelectRAM和分布式RAM(DistributedRAM),以及BlockRAM的使用方法,优化存储器性能。

3. **时钟管理和信号分配**:

- **时钟资源**:详细讨论了全局时钟(GlobalClock)、时钟多路复用器(CLKMUX)、DCM(数字时钟管理器)以及DCI(数字时钟接口)的使用,以确保系统时钟的有效管理和优化。

- **I/O管理**:介绍了IOB(输入输出块)的结构和功能,包括SelectI/O的选择,以及如何有效地分配I/O资源。

4. **特定资源利用**:

- **乘法器资源**:分析了乘法器的使用,可能包括专用硬件加速或算法优化。

- **Shift Register LUTs (SRL)** 和其他逻辑单元(如MUXFX、SOP、CarryLogic和ArithmeticLogicGates)的运用,强调了在有限资源下的高效利用。

5. **编码风格与器件特性**:

- **器件结构与编码风格**:探讨了不同架构(ASIC和FPGA)对编码风格的影响,以及如何适应Virtex-II等特定器件的特性。

- **代码风格比较**:提供了不同编码风格的对比,以指导设计师根据器件特性选择最有效的实现方式。

通过这份文档,华为的技术专家分享了他们在Xilinx FPGA高级设计中积累的经验,旨在帮助工程师们提高设计效率,减少资源消耗,同时确保系统的性能和稳定性。对于从事FPGA设计的专业人士来说,这是一个宝贵的参考资料。

2020-02-15 上传

2022-09-19 上传

2022-08-08 上传

161 浏览量

点击了解资源详情

点击了解资源详情

2021-07-09 上传

JackeyTu

- 粉丝: 0

- 资源: 2

最新资源

- 行业文档-设计装置-组合不同灵敏度排卵检测试纸半定量测量LH浓度法.zip

- 蓝屏dmp文件分析-易语言

- 150W 数字电子负载全部PCB、SCH设计_智能家居物联网开发PCB设计方案.rar

- Advent-of-Code-2019:我对2019年代码到来挑战的解决方案

- spring-beans-5.3.10.jar中文-英文对照文档.zip

- 全新UI自助图文打印系统源码(含前端小程序源码 PHP后端 数据库)

- 行业文档-设计装置-笔记本电脑支架装置.zip

- demoAES (1)_imageAES_matlab_AES_

- react-jest-examples:React组件的示例笑话测试

- 基于jsp+servlet+mysql网上蛋糕店

- aerosol-observation-analysis:分析和绘图工具,用于探索气溶胶观测

- player-musik:制作音乐播放器很简单

- 行业分类-设备装置-一种适用于日光温室的主动蓄放热墙体.zip

- fixfridge:Web应用程序,用于从传感器实时记录数据

- httpcore-4.4.14.jar中文-英文对照文档.zip

- 毕业设计java校园疫情防控系统springbootvueweb有文档源码含文档含教程