CMOS电路分析:与非门与复杂组合逻辑设计

需积分: 9 113 浏览量

更新于2024-07-29

收藏 1.7MB PDF 举报

本文主要探讨了COMS电路中的与非门设计及复杂组合逻辑电路的构建,内容涉及CMOS逻辑门的基本概念、反相器的直流特性、暂态响应、噪声容限以及开关特性。

在COMS电路设计中,与非门是基本的逻辑门类型之一,它结合了N沟道和P沟道金属氧化物半导体场效应晶体管(MOSFET)的优点,可以实现非线性的逻辑功能。与非门由两个互补的MOSFET组成,一个N沟道MOSFET和一个P沟道MOSFET,当所有输入为高电平时,输出为低电平;只有当所有输入为低电平时,输出才为高电平。

反相器是构建逻辑电路的基础,它的直流特性是分析电路性能的关键。电压传输特性(VTC)描述了输入电压变化时输出电压的变化情况。反相器的延迟分析则关注信号从输入变化到输出响应的时间,这对于高速电路设计尤其重要。在VTC中,输入高电压VIH和输入低电压VIL定义了逻辑1和逻辑0的阈值,而输出逻辑1(VOH)和逻辑0(VOL)决定了电路的供电电压范围。中点电压VM是VTC上输入等于输出时的电压,反映了逻辑状态转换的中间点。

电压噪声容限是衡量电路抗干扰能力的一个指标,VNMH和VNML分别表示高电平和低电平噪声容限,它们定义了输入电压可以容忍的波动范围而不改变输出状态。中点电压VM的计算涉及到MOSFET的饱和区电流,其值取决于器件尺寸比,对于对称反相器,VM通常设定为电源电压的一半,但可以通过调整尺寸比例来改变VM值,从而影响逻辑输入电压范围。

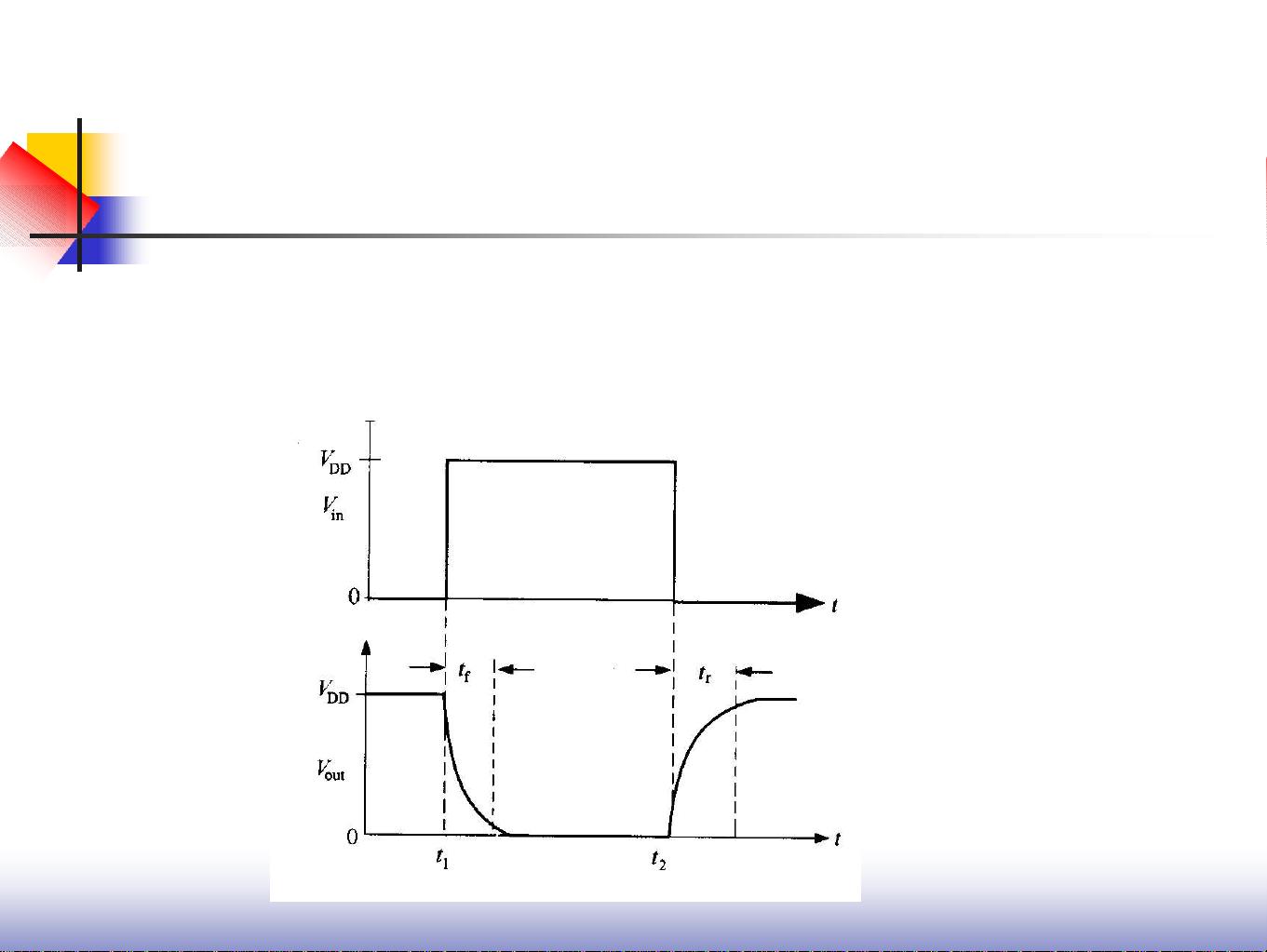

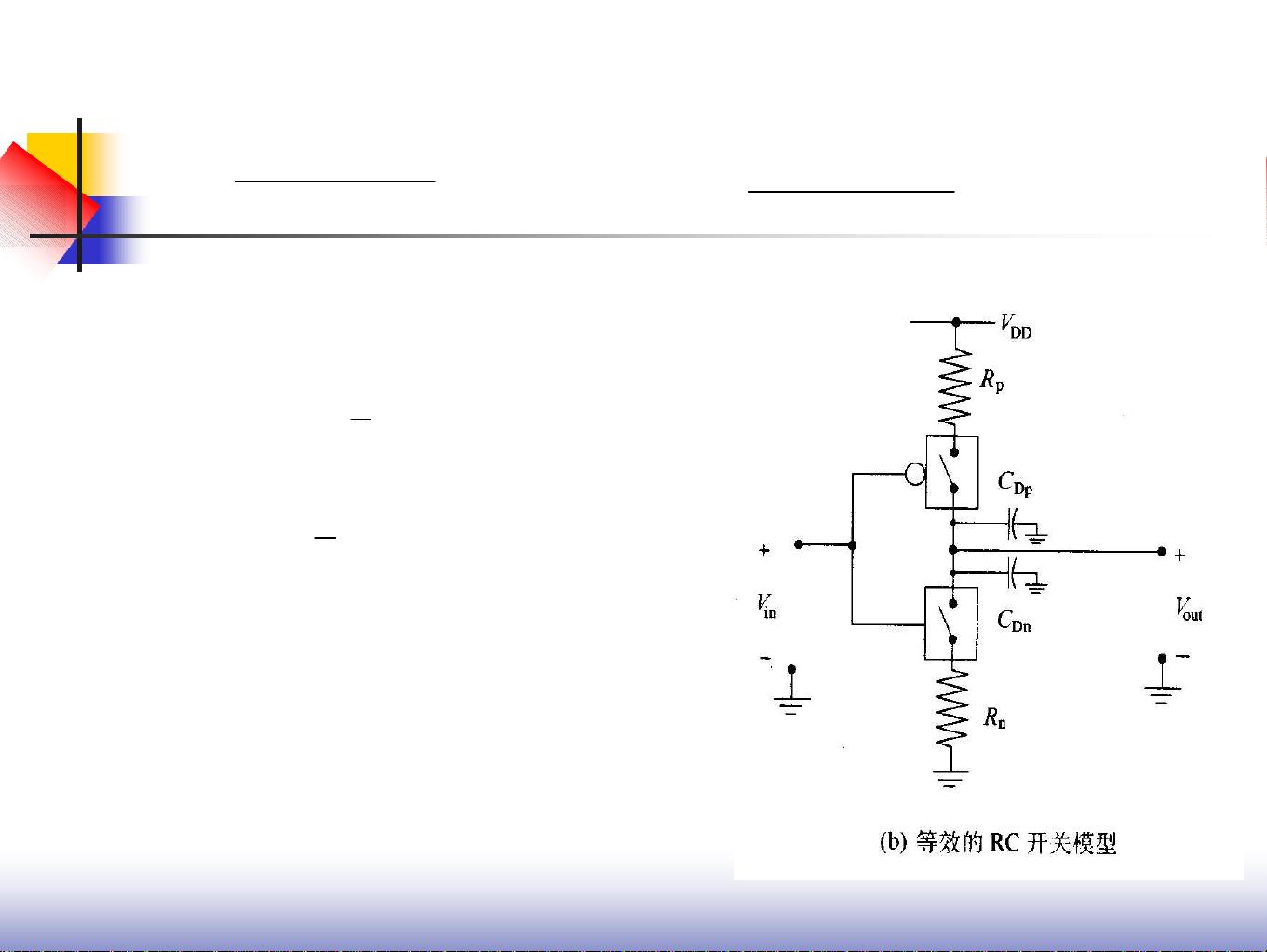

反相器的开关特性涉及到暂态分析,例如上升时间和下降时间,它们定义了输出电压从低电平到高电平或反之的转换速度。快速的上升时间和下降时间可以提高电路的运行速度,但可能会增加功耗。此外,瞬态响应还受到负载电容、阈值电压、驱动电流等因素的影响。

在更复杂的组合逻辑电路设计中,多个与非门和其他逻辑门可以组合以实现任意布尔函数。这些电路通常需要进行逻辑简化、优化和布局,以确保正确性和高效性。优化包括减少门的数量、减小延迟和降低功耗。同时,考虑电路的静态和动态功耗也是设计过程中的重要环节。

COMS电路的与非门设计和复杂组合逻辑电路的构建是VLSI系统设计的基础,涉及电路的直流特性、噪声容限、开关特性和优化策略等多个方面,这些都直接影响着电路的性能、速度和功耗。理解和掌握这些知识对于微电子工程师来说至关重要。

点击了解资源详情

145 浏览量

点击了解资源详情

145 浏览量

1045 浏览量

533 浏览量

169 浏览量

2021-11-13 上传

169 浏览量

dsw0350

- 粉丝: 0

最新资源

- Java使用JavaMail发送邮件详细教程

- Vim中文文档计划:为中文用户便利的翻译工程

- VB实现全屏幕及区域屏幕捕捉教程

- 微软推出apploc-v1.0内码转换工具,支持多语言转换

- 易语言实现x的y次幂计算与大数处理方法

- 东南大学数据库基础教程第三章分享

- 深入浅出软件建模技术与实践

- 大学生简历写作指南:中英文模板集锦

- C++实现简易HTTP请求路由器教程

- JavaScript时间计算方法:掌握时间距离表述

- CentOS 6.x 系统Docker离线安装教程

- 深入理解CCNP BCMSN自学指南卷二

- 汉字转拼音程序:批量及单字转换方法介绍

- 为XP系统提供AMD芯片组AHCI驱动补丁指南

- 简易个人维基:单文件HTML实现离线可编辑

- 易语言实现图片背景色替换的方法与代码示例