MLX91804

Integrated Tire Sensor

3901091804 Page 19 of 100 Preliminary Datasheet

Rev 1.4 Melexis Confidential and Proprietary February/17

4. Digital blocks

4.1 Master scheduler

The Master Scheduler combines 3 controllers: wake-up controller, power management controller and clock

controller.

The wake-up controller is responsible to trigger the transitions to and from the different sleep modes (see

definitions in section 2.1). It uses a wake-up timer which is always active and that can’t be masked.

The power management controller functionality is responsible for correctly sequencing the power-on and

power-off of the different supply domains of the circuit.

The clock controller functionality is responsible to provide the necessary clocks and resets to the Amalthea

platform when required or gate them properly otherwise. It is also responsible to enable/disable the system

different clock sources in order to reduce current consumption as much as possible in the different operating

modes.

4.2 Amalthea MCU platform

The Amalthea platform is an IP-based platform built around a MLX16 core. The platform configuration which

is specific to this system includes the following main (non-exhaustive) features:

MLX16 16-bit RISC microcontroller core with integrated coprocessor (hardware multiplier). The MLX16

core instruction set allows word, byte and bit manipulation. Seven levels of interrupt priority together with

3 bits software priority level provide flexible interrupt handling, while the Protected and User execution

modes together with exceptions detection supports a high security level.

Two 14-bits general purpose timers

Absolute watchdog timer with own MCU independent 1 MHz clock

Extended-counting ADC interface.

Memories interfaces.

Melexis Universal Programming and Test (MUPeT) interface.

The Amalthea platform is supplied by VDIG voltage domain maintained by an internal voltage regulator with

output voltage about 1.7V. The regulator supplies also the HFO generating a clock for the Amalthea platform.

The VDIG regulator is turned off during sleep modes.

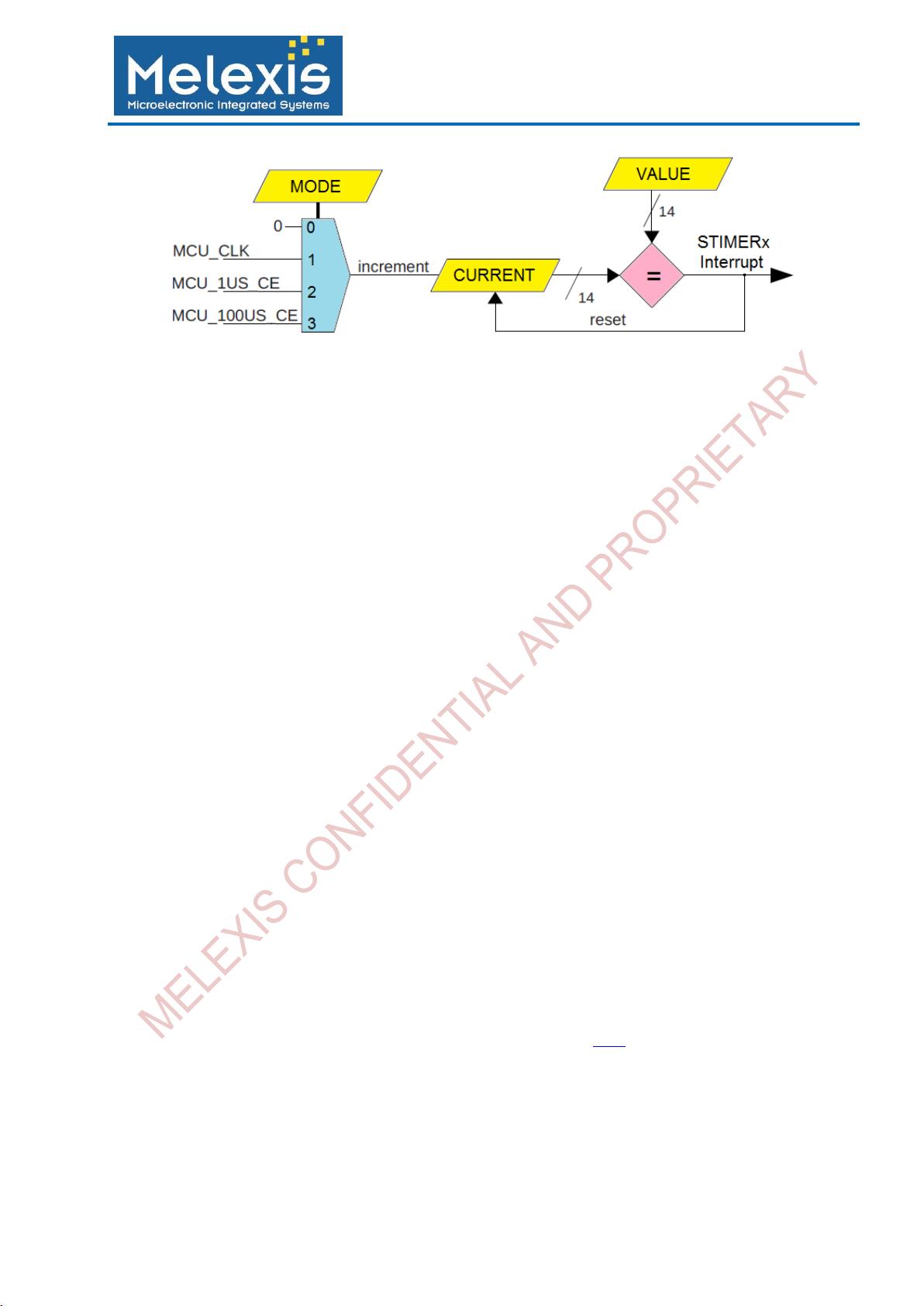

4.2.1 General purpose simple timers

Two available 14-bits general purpose simple timers have similar structure and feature:

14 bits incrementing counter

Generate an interrupt when counter reaches the timer value

Reset counter when it reaches the timer value

Selectable clock enable (MCU_CLK, MCU_1US_CE or MCU_100US_CE)

The timers are represented in the registers map by 2 separate 32-bit blocks STIMER1 and STIMER2. Both

include registers with similar functions. The 14-bit read only register CURRENT reflects a current state of the

timer’s counter. Two unused MSB, allocated in the 16-bit word together with CURRENT, are always equal to

0. The second 16-bit word is used to control a corresponding timer. The 2 MSB of that word define the timer

mode, while the others 14 bits define the timer value (registers names are MODE and VALUE accordingly).

Both timers are based on incrementing counters and both are disabled on a reset. When counter reaches

VALUE, a corresponding interrupt is generating and the counter is reset.