基于VerilogHDL的FPGA自动售货机设计

需积分: 10 26 浏览量

更新于2024-07-29

收藏 123KB PDF 举报

"这篇文档是关于使用Verilog HDL实现自动售货机系统的设计,主要讲解了基于FPGA的软饮料自动售货机的工作原理和设计过程。文档内容包括介绍、有限状态机(FSM)的类型、状态图、Verilog代码实现、测试平台以及输出解释。"

1

章节1:介绍

自动售货机是一种根据投入的硬币金额来分发饮料的机器。它接受镍币(5美分)、一角硬币(10美分)和二十五分硬币(25美分)。只有当收到40美分时,才会分发饮料。如果收到的金额超过40美分,超出部分将作为找零返回。系统输入是硬币,输出是饮料。下一章将探讨如何用状态图表示和绘制状态机。

2

章节2:有限状态机

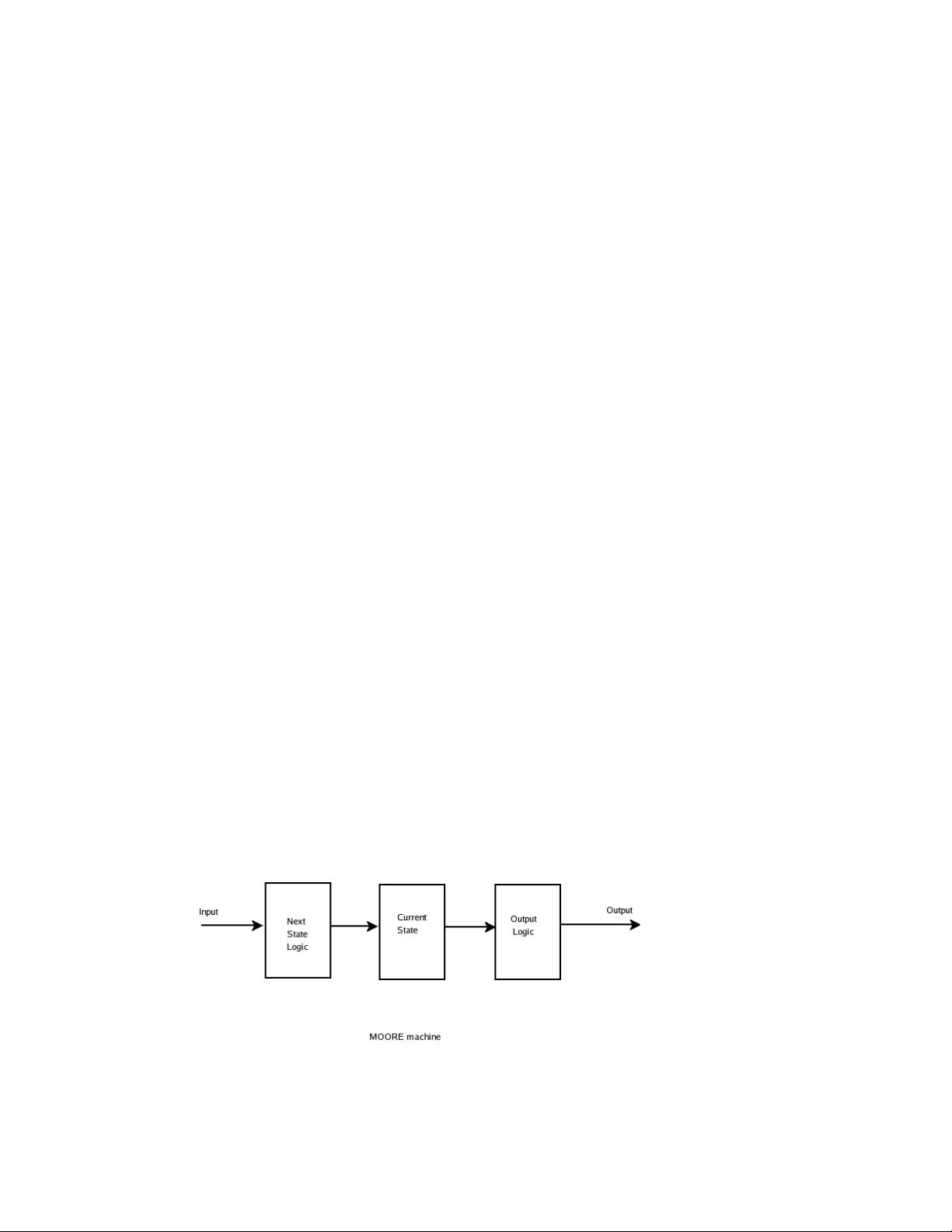

任何顺序数字电路都可以转换为一个状态机,通过状态图表示。在状态机中,每个输出对应于不同的状态,有一个状态寄存器来存储机器的状态,还有一个下一个状态逻辑来决定状态的变迁。

3

章节3:状态机类型

状态机分为两类:Moore型和Mealy型。Moore型状态机的输出只取决于当前状态,而Mealy型状态机的输出则同时取决于当前状态和输入。状态图是描述状态机行为的关键工具,用于定义不同状态间的转换条件。

4

章节4:Verilog代码实现

在这一部分,作者将详细展示如何使用Verilog HDL语言编写自动售货机的状态机代码,包括如何定义状态变量、状态转移逻辑以及与输入和输出的交互。

5

章节5:测试平台

为了验证Verilog代码的正确性,通常需要创建一个测试平台(TestBench)。测试平台模拟各种输入序列,并检查自动售货机的预期输出是否正确。

6

章节6:输出解释

最后,文档将详细解释实际运行中的自动售货机系统会产生哪些输出,以及这些输出如何对应于机器的不同工作状态和操作流程。

这个基于Verilog HDL的自动售货机设计,不仅展示了数字逻辑设计的基本概念,还涵盖了状态机设计、FPGA实现和验证等关键步骤。对于学习硬件描述语言和数字电子设计的学生或专业人士来说,是一个很好的学习实例。

点击了解资源详情

714 浏览量

点击了解资源详情

128 浏览量

1700 浏览量

2023-06-03 上传

2021-03-16 上传

2021-03-19 上传

2021-05-31 上传

EternalPolaris

- 粉丝: 2

最新资源

- Python大数据应用教程:基础教学课件

- Android事件分发库:对象池与接口回调实现指南

- C#开发的斗地主网络版游戏特色解析

- 微信小程序地图功能DEMO展示:高德API应用实例

- 构建游戏排行榜API:Azure Functions和Cosmos DB的结合

- 实时监控系统进程CPU占用率方法与源代码解析

- 企业商务谈判网站模板及技术源码资源合集

- 实现Webpack构建后自动上传至Amazon S3

- 简单JavaScript小计算器的制作教程

- ASP.NET中jQuery EasyUI应用与示例解析

- C语言实现AES与DES加密算法源码

- 开源项目实现复古游戏机控制器输入记录与回放

- 掌握Android与iOS异步绘制显示工具类开发

- JAVA入门基础与多线程聊天售票系统教程

- VB API实现串口通信的调试方法及源码解析

- 基于C#的仓库管理系统设计与数据库结构分析