基于VerilogHDL的出租车计价器设计与实现

版权申诉

出租车计价器的设计是现代电子工程领域中的一个重要应用,特别是在交通自动化和信息技术融合的背景下。本文主要探讨的是采用Verilog Hardware Description Language (VHDL)——一种高级的硬件描述语言,在FPGA(Field-Programmable Gate Array)或CPLD(Complex Programmable Logic Device)平台上,设计一款出租车计价器系统的过程。该设计的目标是实现一个实用且高效的计费系统,能够精确计算起步价、里程费用和等待时间费用。

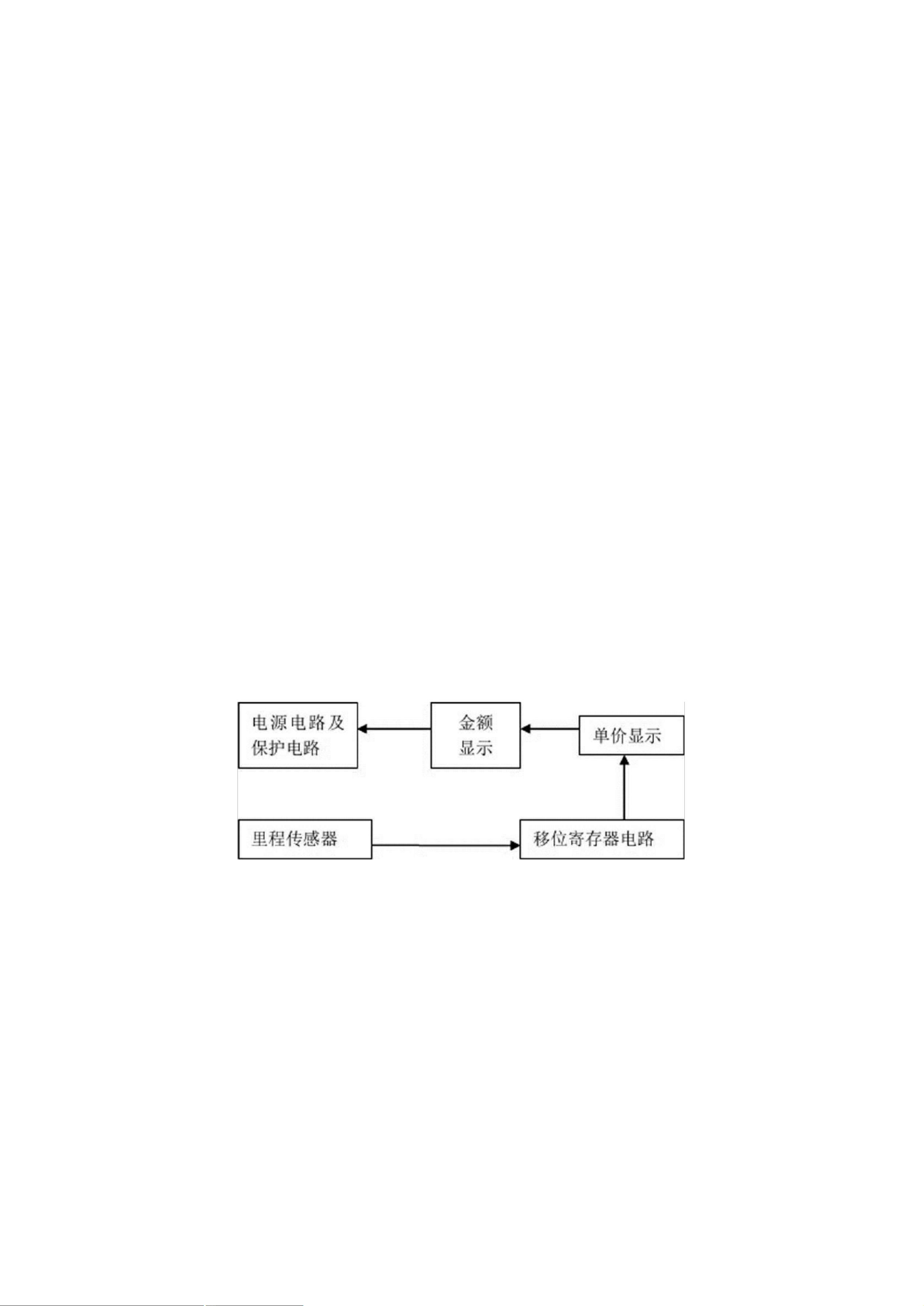

在文章的开头,作者提到了设计背景,即西华大学2009级信息工程专业的学生林竞力于2012年6月6日完成的课程设计项目。设计的关键目标是满足出租车计费的基本功能需求,确保系统的准确性与实时性。Verilog HDL的选择反映了其灵活性和强大的系统描述能力,这使得设计师能够细致地分解和实现各个模块,如分频模块负责时间的处理,计程模块负责记录行驶距离,计费模块计算总费用,计时模块管理等待时间,而动态扫描显示模块则用于清晰地显示费用信息。

文章的“前言”部分概述了设计的总体思路,首先明确设计的要求,这可能包括计价器的功能需求、性能指标以及技术规格。随后,作者进行了方案论证与选择,可能会讨论不同设计方法的优缺点,为何选择Verilog HDL而不是其他语言,以及FPGA或CPLD的优势,如高速运算能力和灵活性。

在“总体方案设计”部分,设计者详细描述了各个模块的具体实现策略,如何通过VHDL语言来编写代码,确保模块间的协作无缝,并能有效利用FPGA的逻辑资源。此外,这部分可能还会涉及系统架构设计,如数据流的处理、输入输出接口的设计以及如何进行有效的错误检测和处理机制。

文章的最后,会详细介绍设计过程中的关键步骤,包括模型验证、仿真测试,以及硬件电路的实现和最终的系统集成。同时,作者还会讨论可能遇到的问题及解决策略,以及设计成果的评估和改进空间。

这篇论文深入探讨了出租车计价器的VHDL FPGA/CPLD设计,不仅展示了理论知识的应用,也体现了实际工程设计的能力。对于那些对硬件描述语言、嵌入式系统和电子工程有深入兴趣的人来说,这是一篇具有实践指导意义的技术文档。

324 浏览量

330 浏览量

228 浏览量

380 浏览量

1004 浏览量

xxpr_ybgg

- 粉丝: 6803

- 资源: 3万+

最新资源

- PL2302驱动.rar

- jotto-testing-project:为使用React构建的简单猜字游戏项目编写测试

- BASS 音频输出设备自动切换-易语言

- coding-notes

- foobarx.github.io

- C# Base64编码和解码 带源码.rar

- LiveTags in every eMail-crx插件

- 自动化码头内集卡作业调度优化.rar

- UITextViewExtras(iPhone源代码)

- JLINKV9.4 PCB-自动升级固件-教程.rar

- 博克

- blogwithaddexperience

- Stocks Market-crx插件

- jsp+mysql图书馆管理系统

- EXDUI2.0日期框扩展,支持时分秒-易语言

- saybeking.github.io