ALTERA MAX+plusII CPLD设计实战教程:三人表决器案例

本资源是一本详细的CPLD/FPGA设计实例手册,主要以ALTERA公司的MAX+PLUS II软件和EPM7128SLC84-15芯片为例,介绍了CPLD设计的完整过程。手册首先阐述了FPGA/CPLD在电子设计领域的关键地位,它们与单片机的重要性相媲美。CPLD是复杂的可编程逻辑器件,而FPGA通常指代基于SRAM工艺的现场可编程门阵列,不同厂商如Xilinx和Altera对产品的命名有所差异。

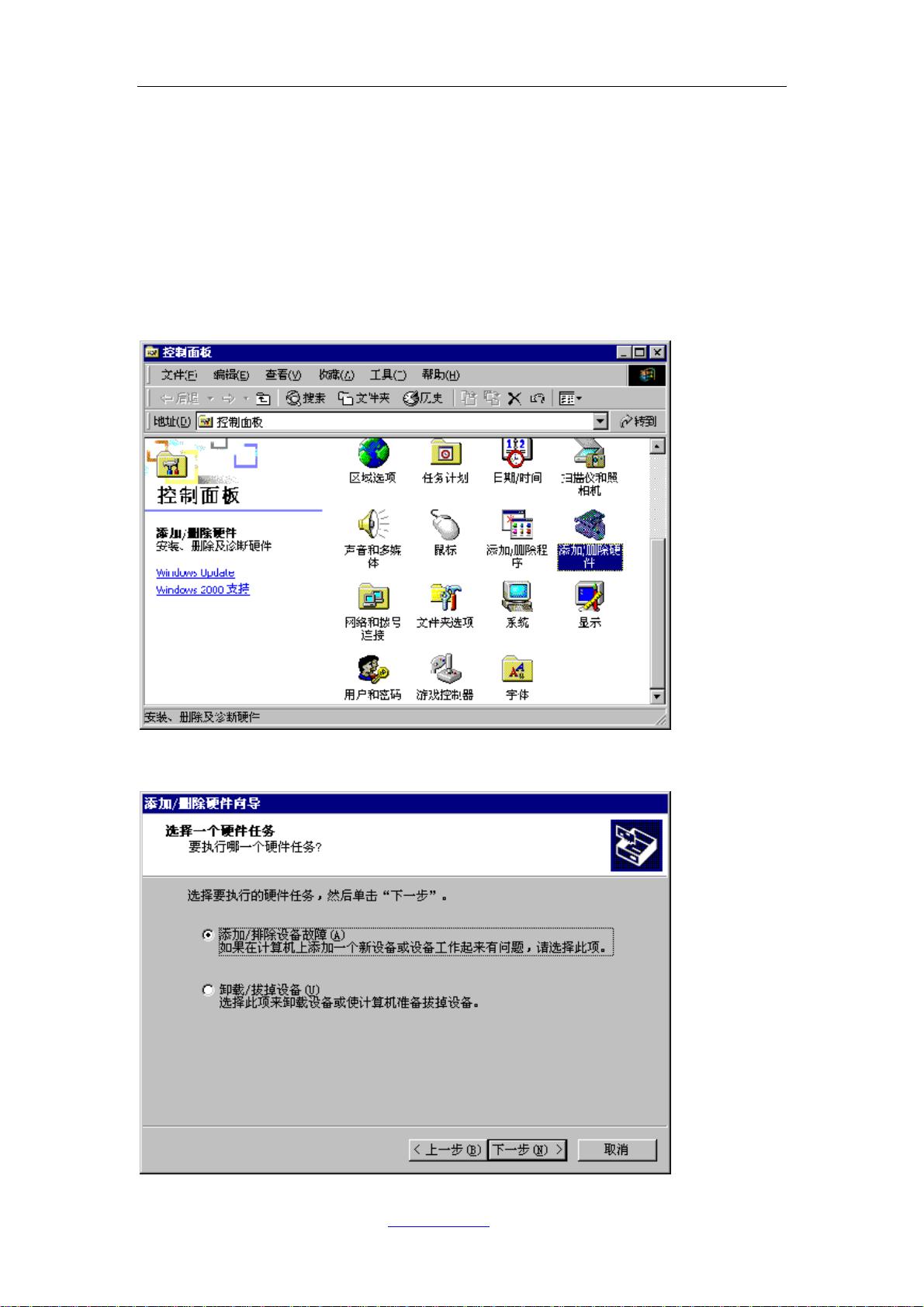

在手册中,章节详细到如何获取和安装MAX+PLUS II软件,包括软件的安装步骤和必要的许可证设置。接着,作者通过实际操作演示了如何使用VHDL语言设计一个三人表决器,涵盖了从打开软件、创建新文档、编写设计文件、编译检查、创建符号、波形仿真以及下载验证等各个环节。此外,还介绍了原理图输入和Verilog-HDL语言设计的方法,以便读者全面掌握CPLD设计的不同手段。

对于初学者或希望提升CPLD设计能力的工程师来说,这本手册提供了实用的工具和技术指导,有助于理解和应用CPLD/FPGA技术进行实际项目开发。通过学习和实践手册中的实例,读者可以深入了解CPLD的设计流程,并逐渐熟练掌握使用ALTERA MAX+PLUS II软件进行硬件描述语言编程和芯片配置的过程。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-03-18 上传

2020-08-05 上传

2014-09-19 上传

2010-11-15 上传

2008-06-13 上传

2010-04-18 上传

dzfdzfdzf

- 粉丝: 0

- 资源: 1

最新资源

- AgileZap

- TagUI:创建TagUI示例以提高生产率

- generator-sails-plugin-hook:Yoeman 生成器创建帆钩,将其自身插入帆结构中

- 毕业设计&课设--趁早(quickearly)早餐外卖微信小程序--方便面的毕业设计.zip

- matlab-(含教程)基于sift特征提取的图像配准和拼接算法matlab仿真

- Excel模板00固定资产明细账.zip

- Hotel-Management-System:Django中的酒店管理系统

- dotfiles:我的dotfiles

- pscc2015:Capstone 2015 - 来自 KUB 与 PSTCC 的合作

- tlvc-api

- 毕业设计&课设--车辆管理系统本科毕业设计,php+mysql+python.zip

- matlab-(含教程)基于传感器融合(UWB+IMU+超声波)的卡尔曼滤波多点定位算法matlab仿真

- Excel模板收据打印模板.zip

- swipe-listener:零依赖性,最小化手势手势的Web侦听器

- chittiBirthday:学习NodeJS和Google云

- github-issue-agent:使用带有令牌的 Github 问题基础结构的 Node.js 项目