模拟CMOS运算放大器设计与Hspice仿真

需积分: 25 41 浏览量

更新于2024-07-31

1

收藏 562KB PDF 举报

"运算放大器设计的详细资料,包括模拟CMOS、CMOS集成电路的设计与Hspice仿真。"

本文档提供了关于运算放大器设计的详细资料,特别关注了使用CMOS技术的模拟集成电路设计。CMOS(互补金属氧化物半导体)是一种广泛用于微电子学的集成工艺,它结合了N沟道和P沟道 MOSFET(金属-氧化物-半导体场效应晶体管),以实现低功耗和高开关速度。在设计过程中,Hspice(高速SPICE)被用作电路仿真工具,帮助设计师验证和优化设计性能。

文档中的第一个问题是一个具体的电路设计挑战:设计一个增益为20的二极管负载的NMOS管作为输入管的共源放大器(CS放大器)。共源放大器是CMOS运算放大器设计中的常见配置,通常用于提供较高的电压增益。设计要求器件的沟道长度为最小工艺尺寸的4倍,这有助于减少短沟道效应,提高器件的性能。

理论推导涉及计算所需的晶体管尺寸以实现指定的增益。在这种情况下,增益是通过调整输入和负载晶体管的宽度与长度比例来实现的。文档中提到,为了达到20的增益,采用了PMOS作为负载,因为这样可以简化分析,忽略沟长调制效应和体效应。设计者还指出,由于沟道长度要求,选择了0.35微米工艺,并根据设备模型计算了N沟道和P沟道晶体管的宽度。

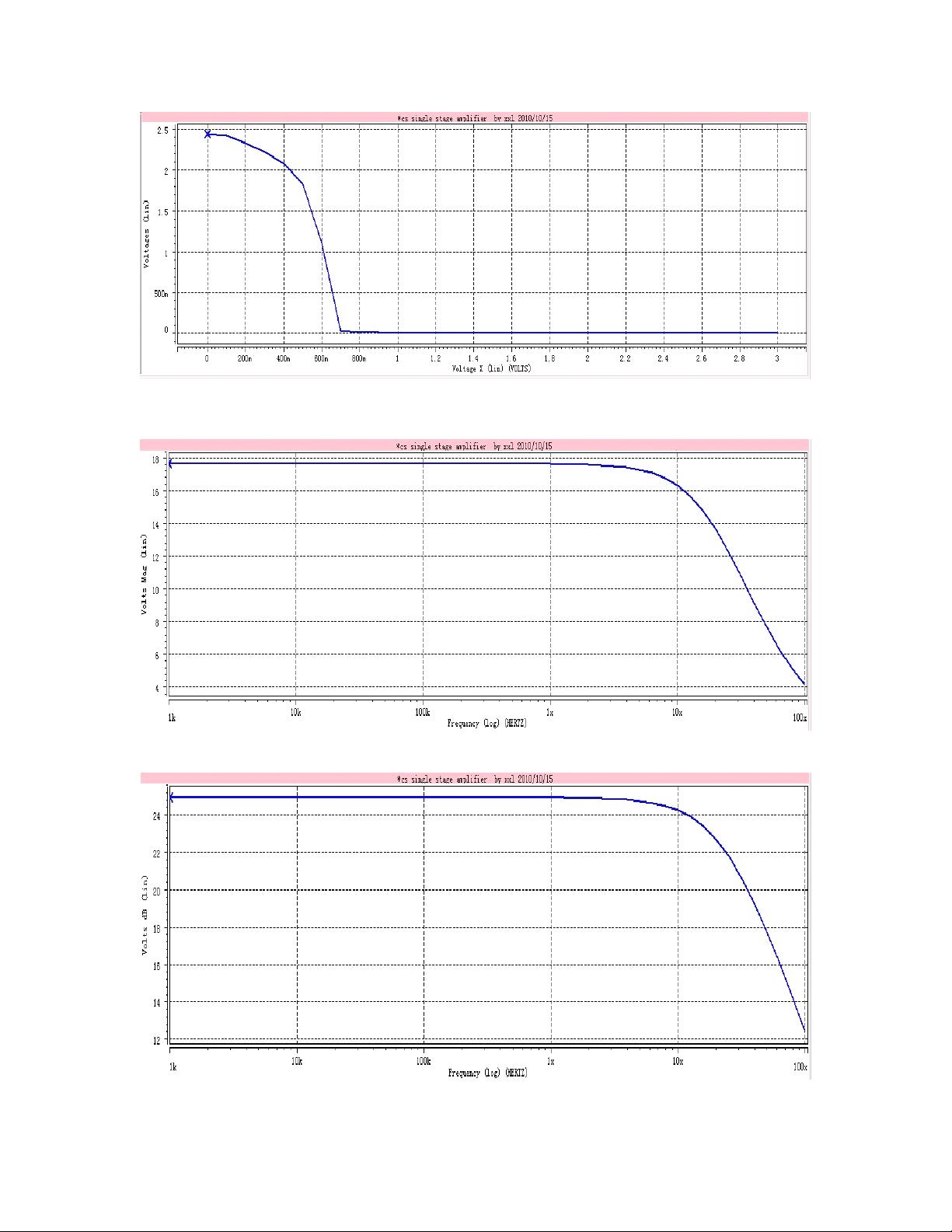

通过Hspice仿真,设计者可以得到电路的输出电压与输入电压的关系,这是验证电路性能的关键步骤。此外,获取小信号增益波形对于分析频率响应至关重要。这个波形以分贝(dB)表示增益,并以对数尺度的频率(log Hz)为横坐标。这些数据可以帮助确定放大器的带宽和稳定性。

文档还探讨了如何基于相同的电路结构设计一个增益为40的CS放大器。这通常涉及到改变晶体管尺寸的比例,可能还需要考虑其他参数如偏置电流或负载电阻的调整,以保持电路的稳定性和线性工作区域。

这份资料提供了运算放大器设计的基础知识,包括CMOS工艺的理解、使用Hspice进行电路仿真的方法以及增益调整的理论。这对于学习者掌握模拟集成电路设计的基本技能是非常宝贵的。

740 浏览量

699 浏览量

203 浏览量

285 浏览量

117 浏览量

102 浏览量

280 浏览量

328 浏览量

chenlong12580

- 粉丝: 620

- 资源: 16

最新资源

- ShopXO免费开源商城 v2.2.0稳定版本

- 易语言学习-SWF制作支持库1.1(静态版).zip

- RangeBlack

- barcode-pda.rar

- It-s-Nothing:我什么都没告诉你

- 消息app相关图标 .fig素材下载

- boostrap-alerts:简单的Meteor JS boostrap警报-在https上查看

- analyzer-ik-7.4.0.zip

- 行业文档-设计装置-一种剑杆上轴轴盘固定装置.zip

- PixetlHard

- 易语言学习-超级加解密支持库1.0#3(08.11.1).zip

- 剧集:使用django,bootstrap4构建的自托管电视节目剧集跟踪器和推荐器

- calculator:这是一个简单的计算器

- tailwind-cinema:使用NEXT.js和Tailwind CSS设计的影片选择器界面

- login_demo_gin.rar

- ballReflection