FPGA实现RS-232串口通信:Quartus+Synplify+ModelSim流程详解

需积分: 0 60 浏览量

更新于2024-07-22

收藏 251KB DOC 举报

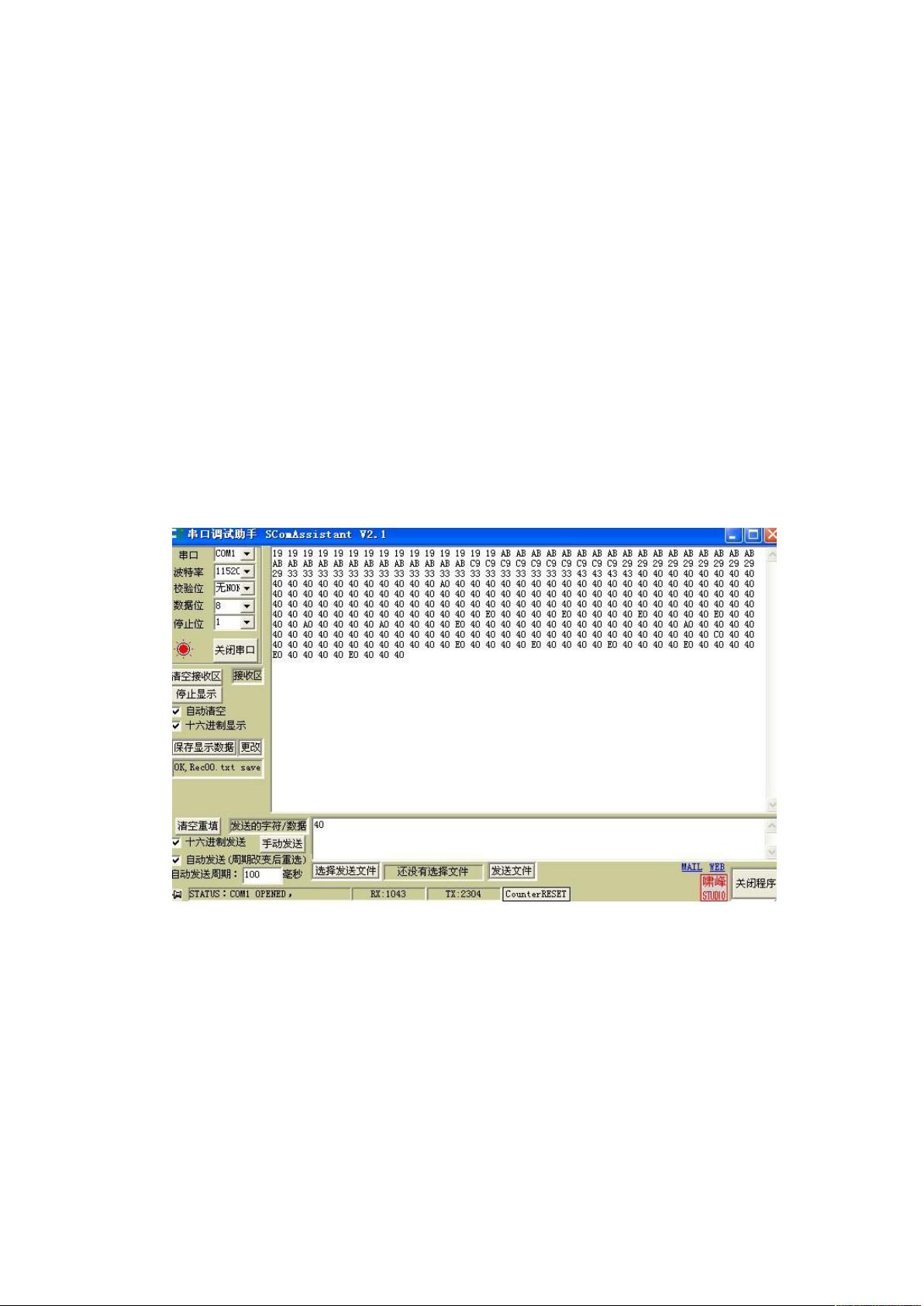

本文档详细介绍了如何使用FPGA(Field-Programmable Gate Array)通过Quartus、Synplify和ModelSim工具进行RS-232串口通信的实现过程。以下是整个步骤的详细解析:

1. **文本程序输入(Verilog HDL)**:

文档开始介绍了一个名为`trans`的模块,它在Verilog Hardware Description Language (HDL)中定义了发送端的功能。模块包括输入信号如时钟(clk)、复位(rst)、发送开始信号(TxD_start)以及待发送数据(TxD_data)。输出端有发送数据线(TxD)和发送状态(TxD_busy)。模块内部使用寄存器(如TxD_dataReg和state)来确保数据的稳定传输,以及参数化了时钟频率(25MHz)和波特率(115200 bps)。

2. **功能仿真(ModelSim)**:

在设计阶段,作者强调了使用ModelSim进行功能仿真的重要性,这是为了验证Verilog代码的逻辑功能是否正确。创建一个TestBench是必要的,用于驱动模块中的输入并观察输出结果,以确保串口数据的发送和接收符合预期。

3. **综合(SynplifyPro)**:

一旦逻辑设计完成并通过功能仿真,下一步是使用SynplifyPro进行综合。这个过程将Verilog代码转换为硬件描述语言的物理实现,生成网表文件,以便在特定的FPGA上进行布局和布线。

4. **布局布线(Quartus II)**:

在Quartus II中,选择的FPGA器件模型决定了具体的实现细节。用户需要将综合后的网表导入到该器件中,进行逻辑布局和布线。同时,要估算电路的实际时延,这对于保证串口通信的正确性和实时性至关重要。

5. **时序仿真(ModelSim)**:

最后一步是进行时序仿真,这基于之前估计的时延,以确保在实际的FPGA运行环境下,发送和接收数据的时序符合RS-232标准。这涉及到对模块在不同时钟周期内行为的精确分析,以确保串口通信的稳定性和可靠性。

FPGA实现RS-232串口通信是一个系统级的设计过程,涉及从逻辑设计、功能验证到实际硬件部署的各个环节。理解并熟练掌握这些步骤对于在实际应用中设计和优化高性能的串口通信系统至关重要。通过使用Quartus、Synplify和ModelSim等工具,可以确保设计的高效性和准确性,满足工业级通信的需求。

2022-11-29 上传

2012-08-02 上传

2021-10-10 上传

2022-10-19 上传

2022-10-19 上传

2020-06-21 上传

2022-09-21 上传

2022-10-19 上传

chaoyang1991

- 粉丝: 0

- 资源: 5

最新资源

- vhdl实现三人表决器

- java struts教程

- 如何实现SQL SERVER 2008 的故障转移群集

- s60系列应用框架手册.pdf

- Hibernate开发指南

- JavaScript高级编程(CHS)

- DWR中文文档.pdf DWR中文文档.pdf

- 基于stc单片机出租车计价

- 深入了解MFC中的文挡/视结构.PDF

- 电子元件基础教程,本文简单介绍了一些电子元器件的概念和特性,对初学者有一定的帮助。

- arm architecture reference manual

- 《ZigBee概述》(中文版)

- Reversing C++

- 图的遍历#include <stdlib.h>

- Toad for Oracle

- ORACLE官方SQL教程中文版