高速PCB设计:解析传输线效应与仿真策略

90 浏览量

更新于2024-09-01

收藏 312KB PDF 举报

随着电子系统设计的快速发展,特别是随着电路工作频率的不断提升,PCB技术中的高速电路传输线效应变得越来越关键。设计师们现在面临着100MHz甚至更高频率的电路设计挑战,例如总线频率可达50MHz或以上,部分甚至超过500MHz。这样的高速工作条件对电路板设计提出了新的要求,因为传统的设计方法在面对传输线效应和信号完整性问题时可能会失效。

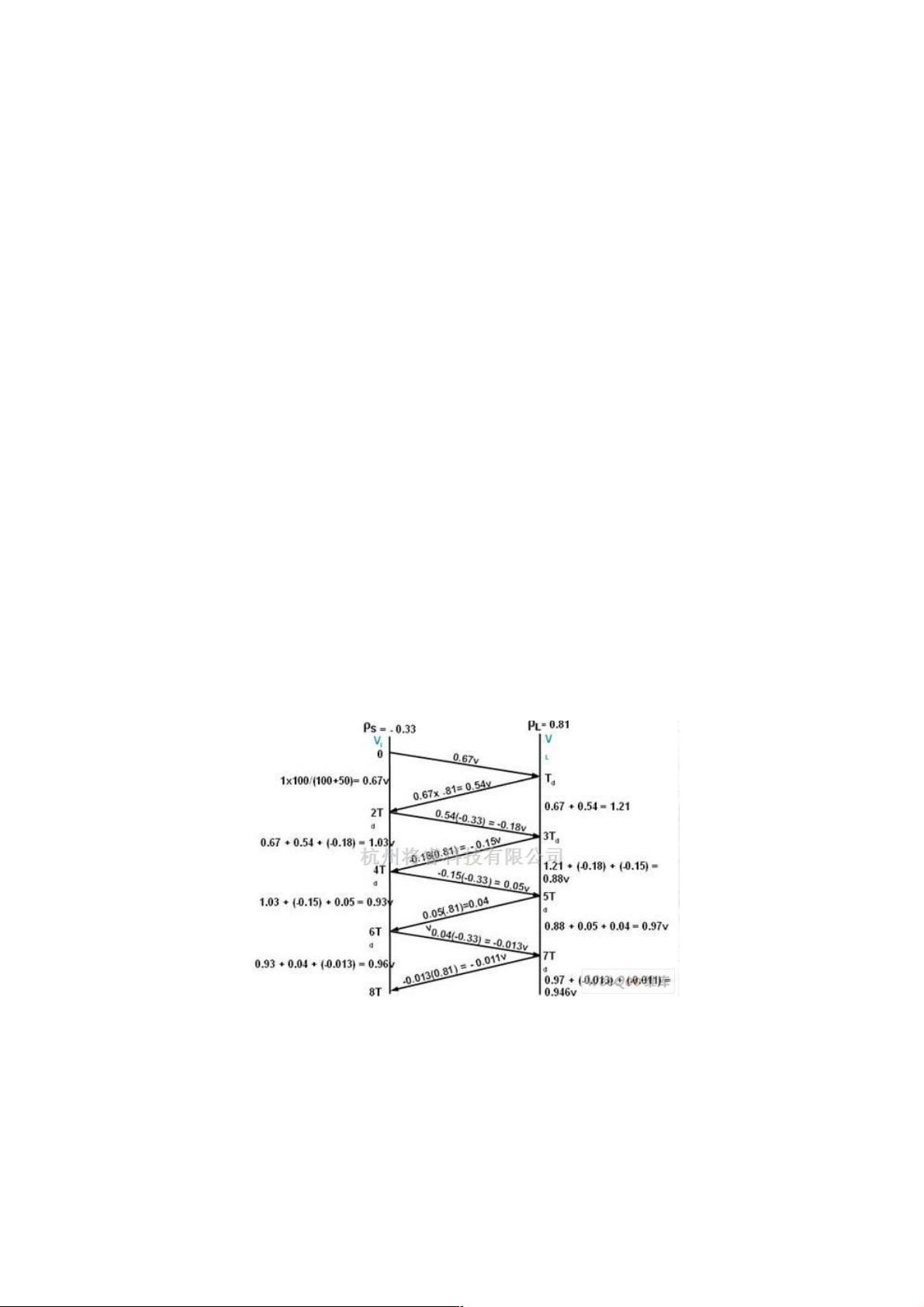

传输线效应是高速电路设计中一个主要的关注点,它包括反射信号、延时和时序错误、过冲(上冲/下冲)、串扰以及电磁辐射等问题。反射信号是由于走线没有正确的终端匹配,信号在传输过程中遇到不匹配的终止点会反射回来,导致信号失真,可能引发设计失败并增加噪声敏感性。为了减少反射,设计者需要优化线路长度和终端匹配。

延时和时序错误是高速信号传输中不可避免的,快速变化的信号可能会导致接收端的时钟和数据同步出现问题,这对电路的整体性能至关重要。过冲现象发生在信号超过其最大允许电压范围,可能导致数据错误,而下冲则是信号下降速度过快,可能导致信号丢失。

串扰是指相邻信号线之间的相互干扰,当两条信号线靠近且频率相近时,一个信号可能会耦合到另一个信号,影响其准确性和可靠性。电磁辐射则是在高速信号传输过程中,由于电流的变化产生的电磁能量,可能对周围设备或系统造成干扰,影响整个系统的电磁兼容性。

解决这些高速电路传输线效应的关键在于采用高速电路信号质量仿真和先进的物理设计软件。通过仿真,设计师可以预测并分析信号行为,优化走线布局、增加接地策略、改善终端匹配等措施来减少效应。此外,选择低噪声、高带宽的器件,以及合理的布线规则和信号规范也是必不可少的。

总结来说,高速电路设计不仅仅是关于提升电路速度,更是对信号完整性、信号质量、电磁兼容性等多方面的要求。掌握和应用传输线效应分析与处理技术是现代电子系统设计师必备的技能,对于确保高性能和可靠性的电路板设计至关重要。

130 浏览量

2020-08-20 上传

2020-07-15 上传

2024-11-03 上传

2024-11-06 上传

2024-11-01 上传

2024-11-01 上传

2024-11-07 上传

2024-11-02 上传

weixin_38679651

- 粉丝: 6

- 资源: 934

最新资源

- joglohub:博客平台

- AndroidApp:尝试 Android 开发

- 行业分类-设备装置-一种接口扩充装置及其控制方法.zip

- YUV转H264代码 运行于ubuntu系统

- metadata-automation:CLOSER启动的元数据和机器学习工作的网站

- arm.rar android平台可运行的ffmpeg库

- rollup-federation:汇总捆绑器中的模块联合

- 百度向安卓推送消息SDK

- 预测房屋价格

- zset:golang中的排序集

- nginx-1.6.3.zip

- springboot的java

- News-Aggregator-Site:一个可以在一个地方访问所有喜爱的新闻媒体的站点

- date-fns-jalali:贾拉利日历的现代JavaScript日期实用程序库

- 行业分类-设备装置-一种接口调用方法、装置及终端.zip

- tasks