硬件EMC设计规范:抑制电磁干扰的关键策略

需积分: 50 194 浏览量

更新于2024-09-09

1

收藏 138KB PDF 举报

"硬件EMC设计规范"

在电子设备的设计中,硬件EMC(Electromagnetic Compatibility,电磁兼容性)设计规范是至关重要的,它确保设备在运行时不会受到电磁干扰,同时也不会对外部环境产生干扰。本规范旨在提供一些基本的EMC设计原则和策略,帮助硬件工程师在开发过程中避免电磁兼容问题。

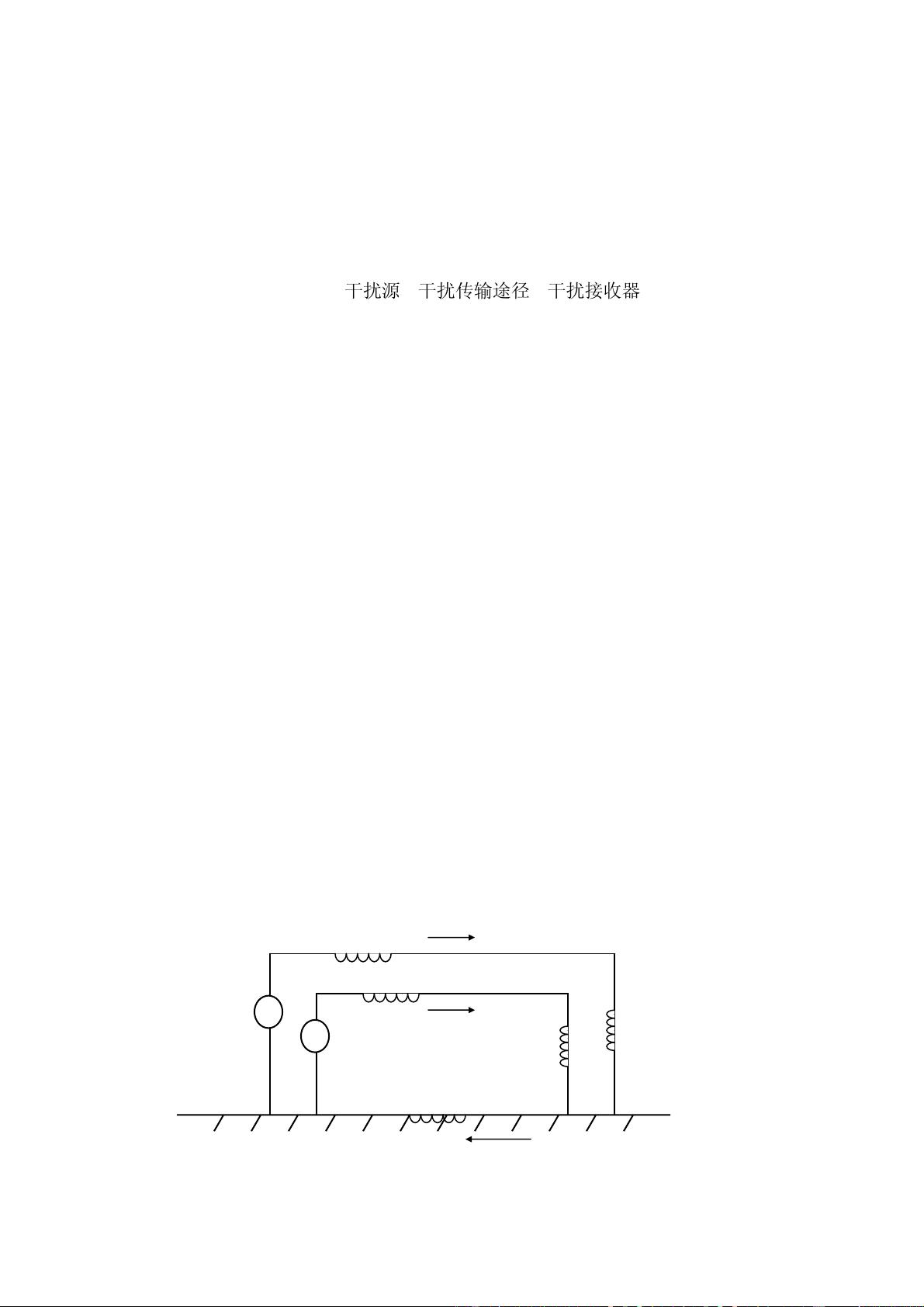

电磁干扰(EMI)的产生主要包括三个要素:干扰源、传播路径和敏感设备。为了控制EMI,主要的技术手段是屏蔽、滤波和接地,这三种方法主要用于切断干扰的传播路径。更广泛地说,EMC控制技术还涉及抑制干扰源的发射和增强接收器的抗干扰能力,以及跨学科领域的应用。

该规范强调了在单板设计阶段就考虑EMC的重要性,因为早期考虑可以有效减少后续样机测试中的电磁干扰问题。常见的问题类型包括公共阻抗耦合、串扰、辐射和噪声拾取,这些问题在高速逻辑电路中尤为突出。例如,随着频率的升高,电源和地线的阻抗增加,使得公共阻抗耦合问题更为常见;信号频率越高,通过寄生电容的耦合效应更显著,导致串扰;信号回路尺寸与时钟频率相似,可能导致强烈的辐射;而阻抗不匹配则会引起信号反射。

针对这些问题,规范提出了一系列的解决策略和设计考虑:

1. 五一五规则指出,当时钟频率超过5MHz或脉冲上升时间小于5ns时,应使用多层PCB板,以减小电磁干扰。

2. 不同电源平面不应重叠,以减少耦合。

3. 针对公共阻抗耦合,建议模拟与数字电路分开并单点接地,使用宽电源线和短印制线,以及适当的去耦电容。

4. 减小环路面积和两环路的交链面积,降低辐射。

5. 优化电源线的特性阻抗Z0,使其趋近于无穷大,通过良好的滤波减少发射和提高抗扰度。

在布局方面,规范提供了以下指导原则:

1. 晶振应靠近处理器放置,以减少信号传输距离和潜在干扰。

2. 分区布局,模拟电路和数字电路应占据PCB的不同区域。

3. 高频电路应布置在板边,并按层次排列,以减少对其他部分的影响。

遵循这些设计规范和布局准则,可以有效地提升硬件系统的EMC性能,确保其在复杂电磁环境中稳定可靠地工作。

170 浏览量

246 浏览量

299 浏览量

451 浏览量

2024-11-06 上传

2024-11-06 上传

343 浏览量

zyjhandsome

- 粉丝: 0

- 资源: 37

最新资源

- 基于.Net Core 物联网IOT基础平台

- web-portfolio:从最基础到最高级的五个项目组合

- self-website-manager:个人网站后台管理部分

- Algorithm-my-code-store.zip

- react-native-push-notification:React本机本地和远程通知

- Webui

- 行业文档-设计装置-玉米秸秆发酵分解剂及在制备玉米秸秆猪饲料中的应用.zip

- 鼠标移动到图片上旋转显示大图的jQuery图片特效

- Dreamweaver网页设计-形考任务十

- HP-U盘格式化启动盘工具1571301907.zip

- 现代控制理论讲义

- UltimateAndroidReference:Ultimate Android参考-您成为更好的Android开发者的道路

- iOS 视图控制器 HSDatePickerViewController.zip

- 丹佛斯变频器VLT_FC280_PROFINET通信_GSD文件.zip

- PHP登录系统:执行基本身份验证

- quickstart-android:Android的Firebase快速入门示例