数字化后端流程简介:Innovus与开放访问设计方法

需积分: 6 169 浏览量

更新于2024-06-27

收藏 5.36MB PPTX 举报

在"Introduction-to-the-digital-flow-Back-End.pptx"的演示文稿中,主要探讨了数字后端设计流程在混合信号应用中的集成,特别是在小规模逻辑核心(约50,000个实例)的实现方面。该文档针对的是一个混合信号ASIC设计环境,采用数字上层(Digital on Top, DoT)或混合信号(Mixed Signal, MS)设计方法论,强调了开放访问(Open Access, OA)设计原则。

内容重点涵盖了以下几点:

1. **动机与起点**:介绍了实施数字块后端流程的方法论,目标是为小型逻辑核心提供一种适合的起点。这个流程适用于需要考虑时序约束的复杂设计。

2. **预置条件**:对于后端数字流,关键组件包括互操作性设计包(Interoperable PDK),如 Virtuoso 流程或专为数字工具和模拟工具设计的通用 .lib 文件。此外,需要使用兼容的工艺技术文件(Common OA tech file 和 Common qrctech file)以确保工具间的一致性和准确提取。

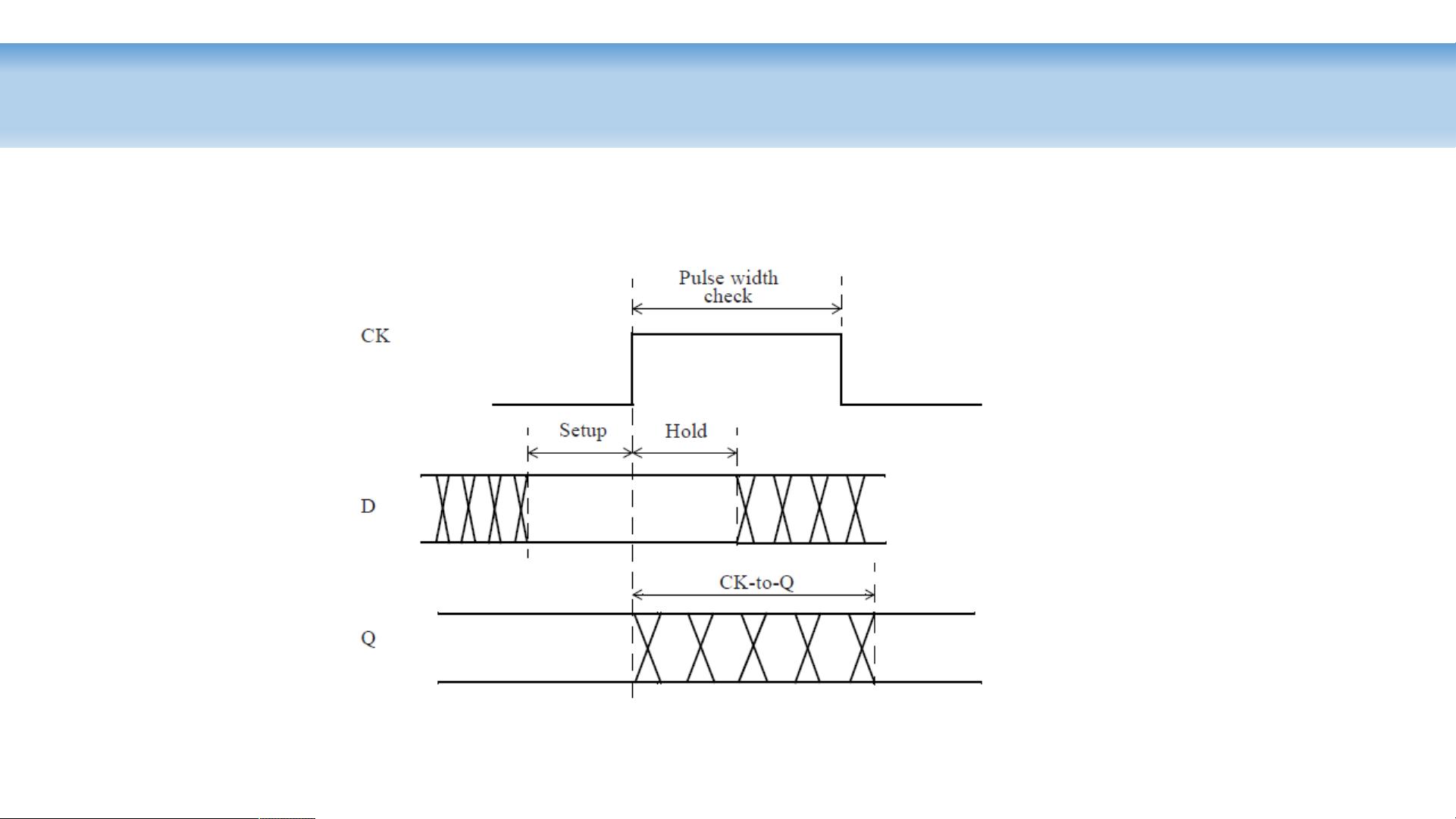

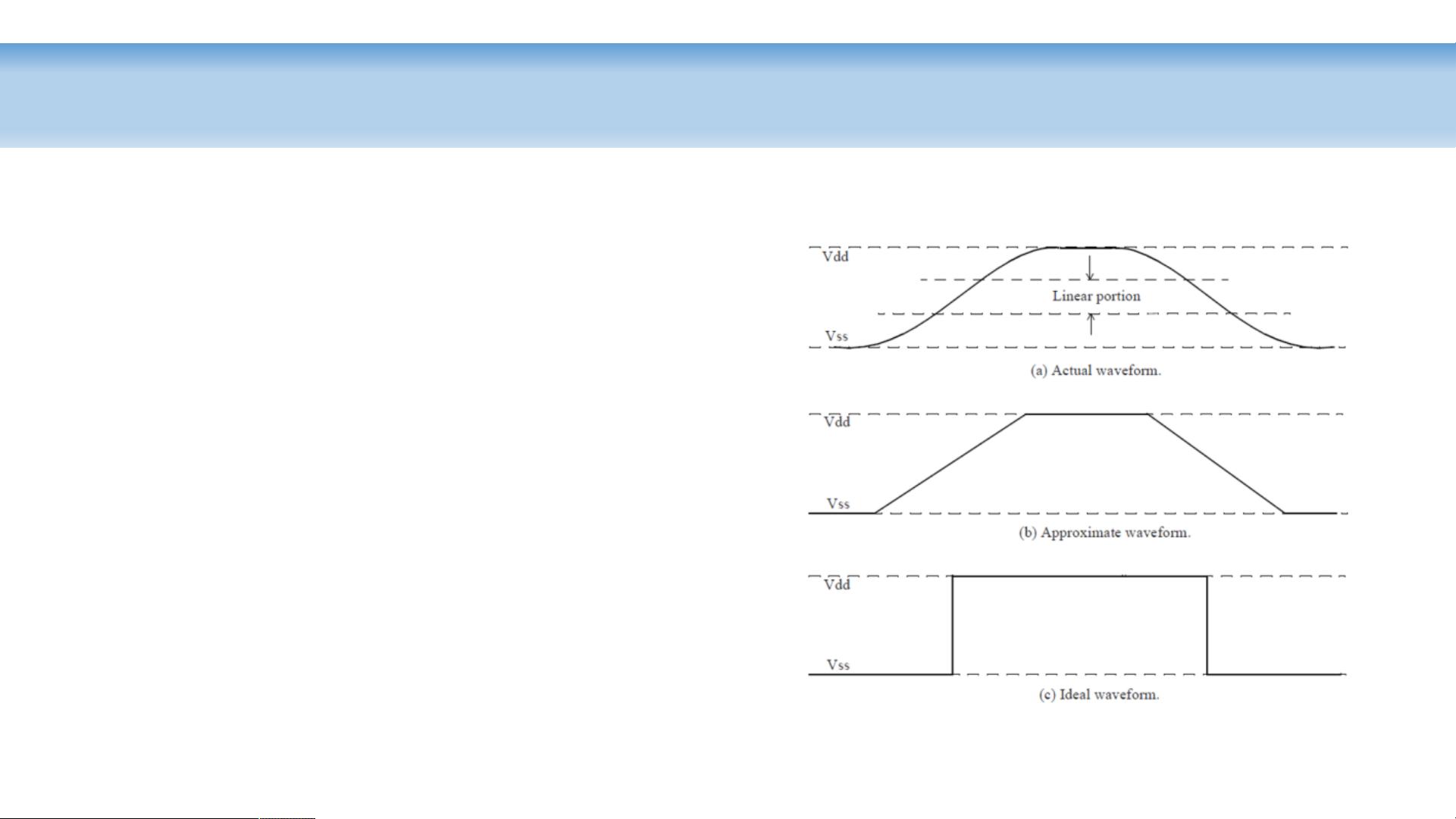

3. **可合成的网表**:为了确保可合成性,功能性网表必须遵循规则,比如为同一寄存器选择上升沿或下降沿触发,避免文本文件中的读写操作,禁止使用显示消息,以及限制使用信号延迟,仅允许使用时钟周期进行同步。

4. **抽象视图与 Liberty 文件**:后端设计流程还涉及到抽象视图的使用,如MMMCview,以及与硬件行为模型(Liberty files)的交互,这些文件用于精确描述器件行为和性能。

5. **工具限制与指导**:文档强调了代码规范,如禁止测试台使用读取或写入文本文件、禁止显示消息,以及特定工具命令如nc_mirror等。这些限制旨在保持设计的简洁和一致性。

总结来说,这份文档详细地阐述了在混合信号ASIC设计环境中,如何通过使用互操作性PDK、可合成的网表和开放访问设计原则来实施后端数字流程。特别关注的是确保设计质量,遵循严格的编程规范和工具使用指南,以应对复杂的时序约束并优化性能。这对于任何希望在类似背景下进行数字设计的工程师来说都是宝贵的知识资源。

2022-06-14 上传

2021-09-14 上传

simuyuwan

- 粉丝: 4

最新资源

- Servlet核心技术与实践:从基础到高级

- Servlet核心技术详解:从基础到过滤器与监听器

- 操作系统实验:进程调度与优先数算法

- 《Div+CSS布局大全》教程整理

- 创建客户反馈表单的步骤

- Java容器深度解析:Array、List、Set与Map

- JAVA字符集与编码转换详解

- 华为硬件工程师的手册概览

- ASP.NET 2.0 实现动态广告管理与随机显示

- 使用Dreamweaver创建网页过渡动画效果

- 创建ASP登录系统:步骤详解

- ASP论坛搭建:资料转义与版主权限管理

- C#新手必读:新版设计模式详解与实例

- 提升网站论坛制作:技术优化与点击计数

- AVR微处理器ATmega32L/32:高级特性和功能详解

- C++实现经典矩阵:螺旋及蛇形排列