Allegro PCB设计约束规则详解与设置

"Allegro_16.3约束规则设置详解"

Allegro PCB设计软件的16.3版本提供了强大的约束规则设置功能,这些规则对于确保电路板设计的质量和可靠性至关重要。约束规则,也称为DRC(Design Rule Check)检查规则,用于验证电路板的布线是否遵循预设的设计标准。

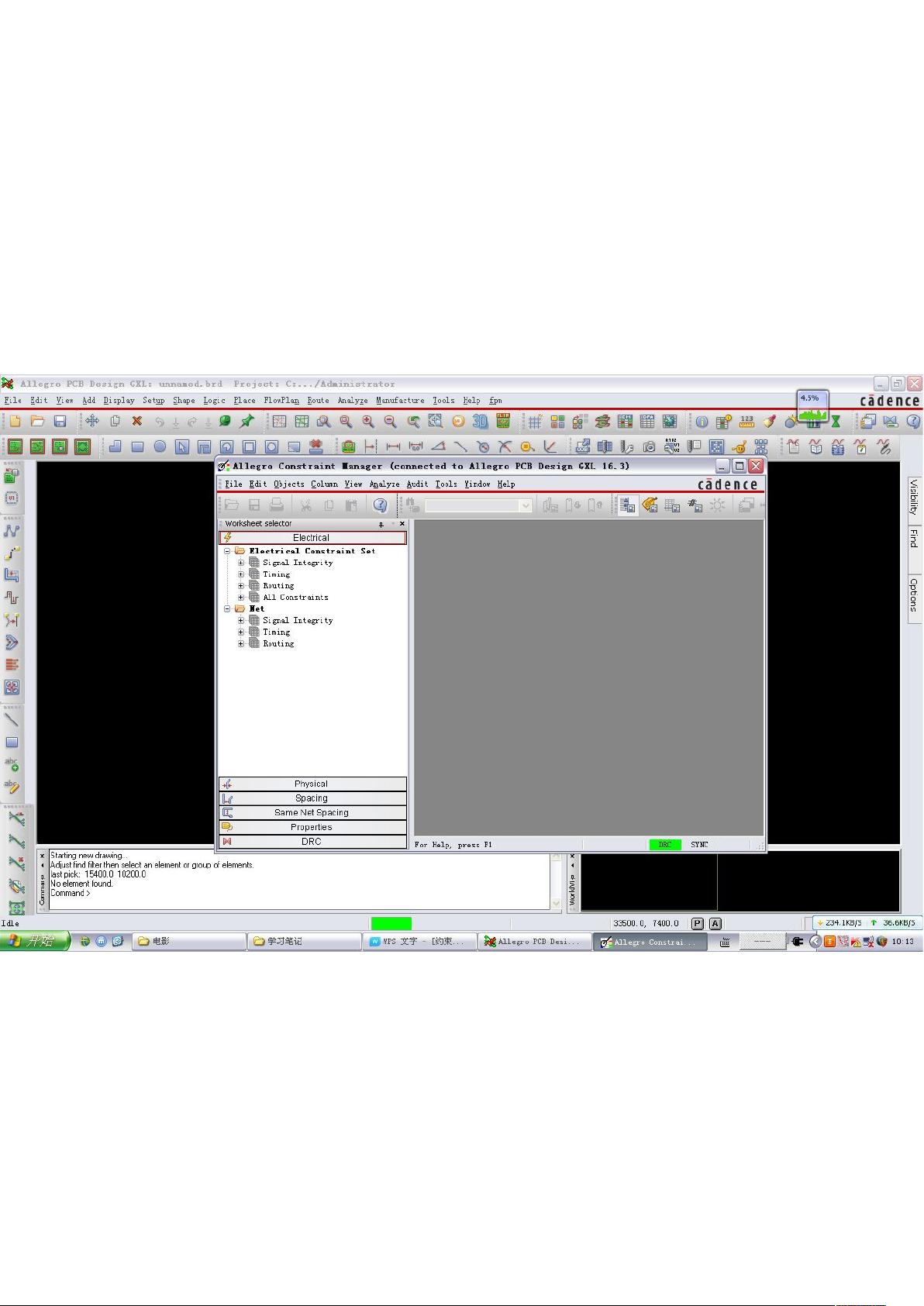

在Allegro PCB中,约束管理器是设置这些规则的核心工具。通过执行“Setup/Constraints/Constraint Manager”命令,用户可以打开约束管理器对话框。该对话框由菜单栏、工具栏、工作表选择区和工作状态报告栏组成,为用户提供了一个直观的界面来定义和管理各种规则。

在工作表选择区,用户可以访问不同的规则类别,例如电气规则、物理规则和间距规则。规则可以按板层、网络或特定区域进行定制。特别地,Net文件夹允许创建不同类型的对象分组,如系统、设计、总线、差分对、扩展网络、网络、相对或匹配群组,同时支持定义ECSet(电气规则集)、PCSet(物理规则集)和SCSet(间距规则集)。

约束对象在Allegro PCB中具有层级结构,包括引脚对、总线和匹配群组。底层对象将继承并优先于上层对象的约束,按照系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对的顺序。

电气规则设置是约束管理器中的一个重要部分,用户可以在Electrical选项卡下为设计或特定网络设定时序规则、信号完整性规则等。例如,可以通过“Objects/Create/ElectricalCSet”命令创建新的电气规则集。信号完整性仿真规则(Signal Integrity)涵盖了一系列参数,如:

1. 电气属性设置(Electrical Properties):包括频率(Frequency)、周期(Period)、占空比(Duty cycle)、时钟抖动(Jitter)等。

2. 反射属性(Reflection Properties):涉及信号在传输线上的反射情况。

3. 单调失真属性(Monotonicity Properties):确保信号在传输过程中的形状保持一致。

4. 初始串扰(Initial Crosstalk)和仿真串扰(Simulated Crosstalk):控制相邻走线间的交互影响。

5. 同步开关噪声(Synchronous Switching Noise):考虑多个开关设备同时切换时产生的噪声。

通过精确设置这些规则,设计师可以确保PCB设计在实际运行时满足高速、高密度和高性能的需求,避免潜在的问题,如信号延迟、反射、串扰和噪声,从而优化电路板的性能和可靠性。因此,理解并熟练掌握Allegro PCB的约束规则设置是每个专业PCB设计师不可或缺的技能。

2013-11-22 上传

2013-01-10 上传

2021-10-19 上传

jm1231

- 粉丝: 112

- 资源: 383

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍