DDS详解:相位累加器驱动正弦波输出与Verilog实现

需积分: 50 111 浏览量

更新于2024-09-12

收藏 505KB PDF 举报

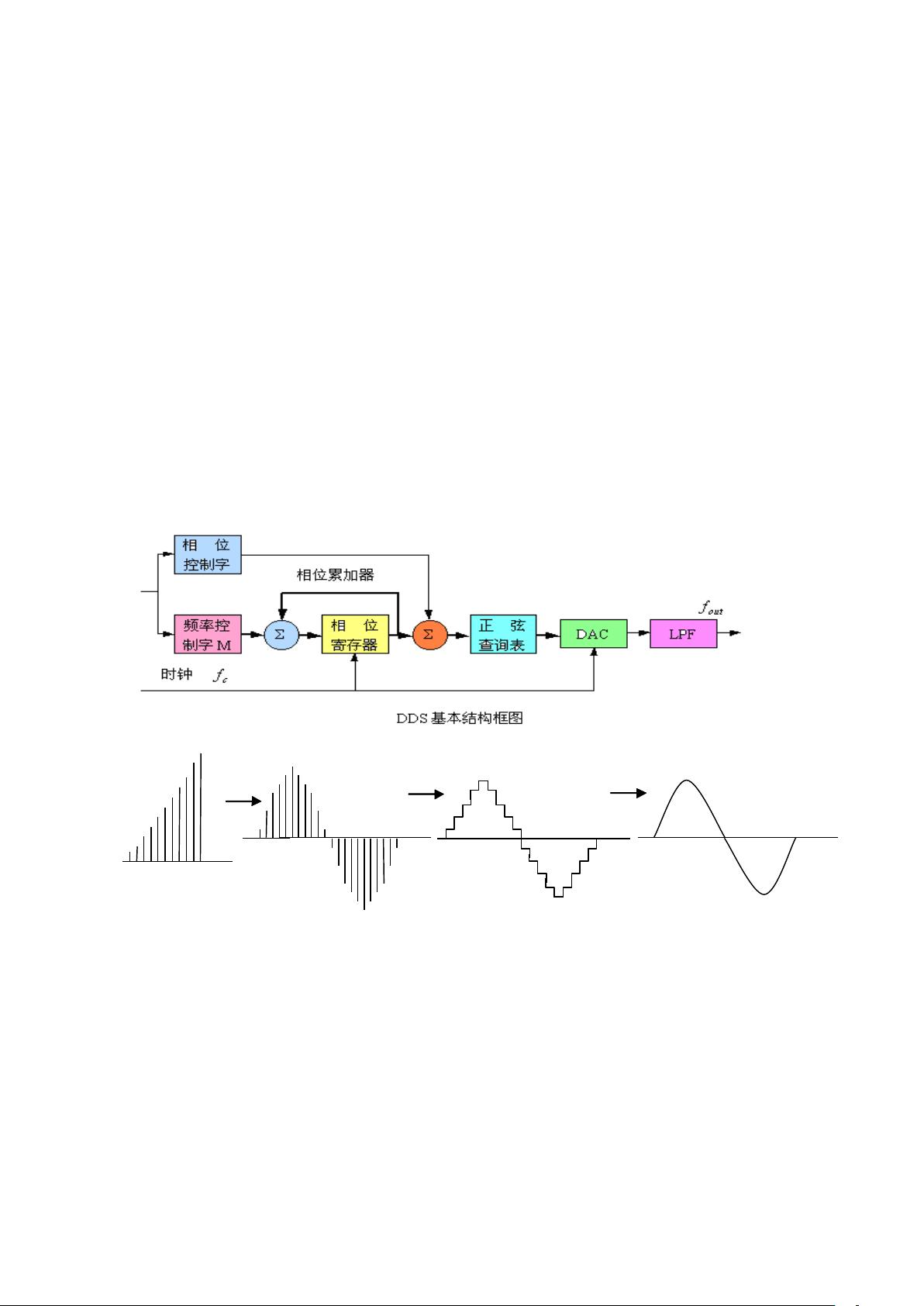

DDS (Direct Digital Synthesis) 是一种数字信号处理技术,用于直接生成连续的模拟信号,特别是在频率合成领域中广泛应用。本文档主要介绍了DDS实现正弦波输出的基本原理及其在Verilog语言中的实现。

1. **DDS原理概述**

- DDS由四个核心组件构成:相位累加器、正弦函数存储器、D/A转换器和低通滤波器。相位累加器负责根据输入的频率设定数据调整相位,通过与位相位寄存器的协同工作,决定输出信号的频率范围和精度。

- 正弦函数存储器(波形存储器)储存了离散化的正弦波幅度,根据查表地址提供数字幅度信号。

- D/A转换器将数字信号转换为模拟信号,以产生所需的正弦波形。

- 低通滤波器则用来平滑输出,消除量化噪声和尖峰效应,确保信号质量。

2. **DDS工作流程**

- 输入一个高稳定性晶体振荡器产生的参考频率,通过频率设定数据控制取样频率,进而影响输出信号的频率。

- 变换过程包括:利用存储的数字波形,通过D/A转换器生成模拟信号;频率调整可以通过改变查表时钟频率或步长实现。

- 相位累加器是关键组件,通过逐次累加相位增量来决定输出波形的当前相位,查询正弦波表获取对应幅度,驱动D/A转换器。

3. **Verilog实现**

- 文档展示了DDS在Verilog语言中的顶层模块设计,包括输入时钟(clk)、两个时钟源clk2、输出正弦波(sin_out)以及相关的控制信号如 dac_en、dac_rst 和 dac_sync。这个模块定义了接口和时序逻辑,用于在数字信号处理阶段实现DDS功能,生成高质量的模拟正弦波。

总结来说,这篇文档提供了DDS技术的深入解析,特别是如何利用Verilog实现DDS系统来精确地生成正弦波。理解并掌握这些原理和技术对于从事信号处理、通信系统或电子设计的工程师来说至关重要,因为它能帮助他们设计和构建高效、精确的频率合成器。

136 浏览量

点击了解资源详情

128 浏览量

1429 浏览量

2022-09-19 上传

157 浏览量

1321 浏览量

130 浏览量

191 浏览量

HX波

- 粉丝: 0

最新资源

- Saber仿真下的简化Buck环路分析与TDsa扫频

- Spring框架下使用FreeMarker发邮件实例解析

- Cocos2d捕鱼达人路线编辑器开发指南

- 深入解析CSS Flex布局与特性的应用

- 小学生加减法题库自动生成软件介绍

- JS颜色选择器示例:跨浏览器兼容性

- ios-fingerprinter:自动化匹配iOS配置文件与.p12证书

- 掌握移动Web前端高效开发技术要点

- 解决VS中OpenGL程序缺失GL/glut.h文件问题

- 快速掌握POI技术,轻松编辑Excel文件

- 实用ASCII码转换工具:轻松实现数制转换与查询

- Oracle ODBC补丁解决数据源配置问题

- C#集成连接器的开发与应用

- 电子书制作教程:你的文档整理助手

- OpenStack计费监控:使用collectd插件收集统计信息

- 深入理解SQL Server 2008 Reporting Services