高速数字电路设计:深入理解信号完整性

需积分: 9 87 浏览量

更新于2024-07-18

收藏 326KB PDF 举报

"高速电路设计,涉及信号完整性的理论与实践,是数字硬件工程师的重要学习内容。"

在高速电路设计中,信号完整性是一个至关重要的概念,它关乎数字系统的稳定性和可靠性。随着技术的进步,电路的工作频率不断提升,使得信号的传输速度和边沿陡峭度增加,传统的低速电路设计方法不再适用。高速电路设计需要考虑更多因素,如无源元件的影响、信号传输的特性以及电磁兼容性等。

1. 高速数字电路简介

高速数字电路涵盖了从电磁继电器到现代集成电路的发展历程,设计上从简单的单层电路板到复杂的多层电路板。高速电路与低速电路的主要区别在于无源元件的效应。在高速系统中,不仅仅是封装,还包括导线、电路板、封装和过孔等都会显著影响信号的传播。当电路工作频率超过一定阈值(如30MHz、25MHz或50MHz),或者信号上升、下降时间变得极短时,就需要考虑高速设计的规则。

2. 信号完整性

信号完整性主要关注信号在传输过程中是否能保持其原始形态,不受干扰。在高速电路中,信号线不能简单视为理想导线,而应作为传输线看待。当走线长度达到信号上升时间的1/6时,分布参数效应变得明显,电压会随时间和位置变化,导致信号畸变、反射和串扰等问题。解决这些问题通常需要采用分布参数模型进行分析。

3. 信号传输的挑战

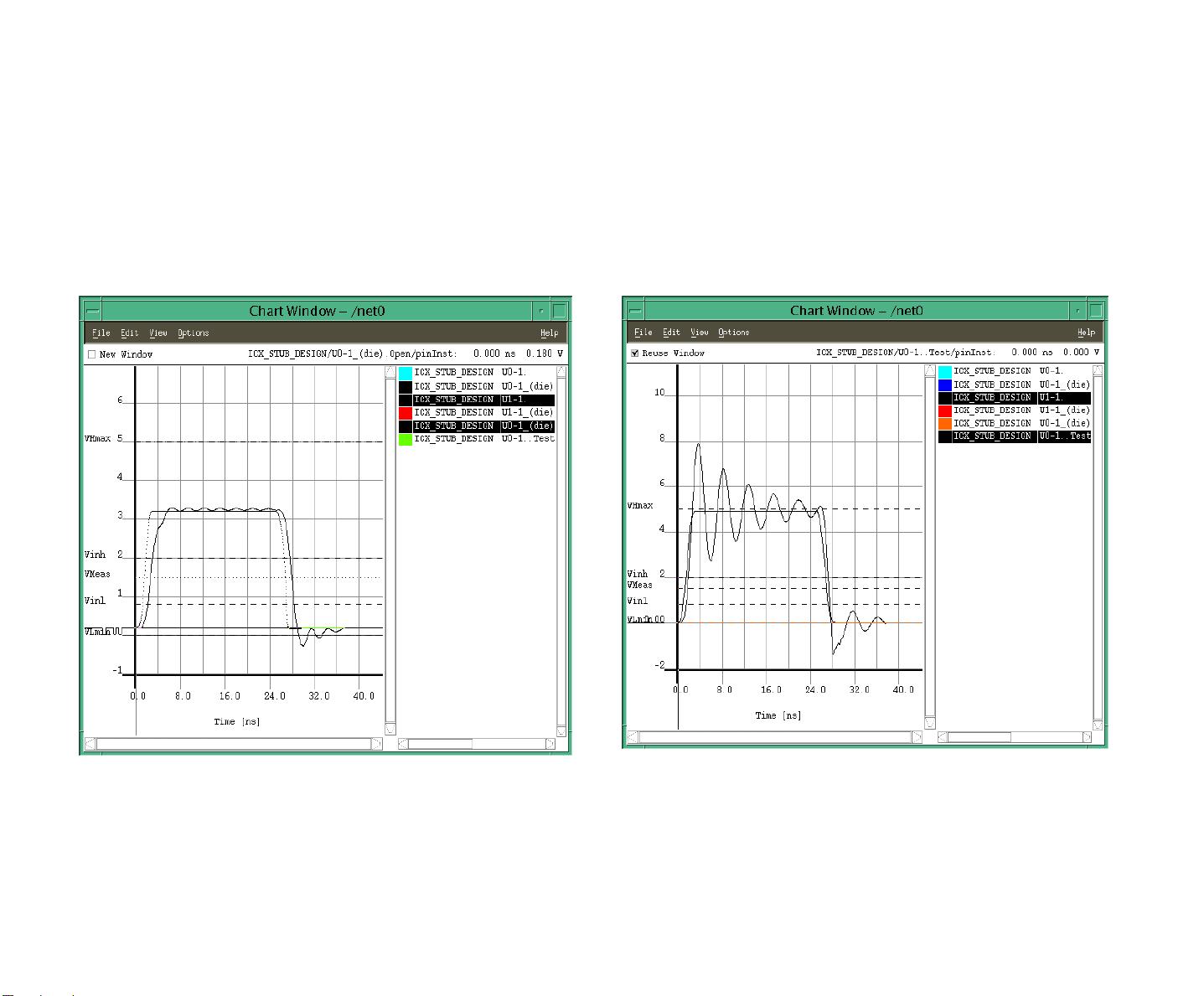

高速电路中的挑战包括振铃、反射和串扰。振铃是信号在传输线末端因阻抗不匹配产生的电压振荡;反射则源于信号在传输线上的反射,可能导致信号失真;串扰是相邻信号线间的相互影响,可能导致误码率增加。这些都需要通过优化布线、合理布局和使用适当的匹配元件来减小。

4. 解决方案与实践

解决信号完整性问题的方法包括:

- 使用正确的PCB材料,降低信号传播的延迟和损耗。

- 设计合理的阻抗匹配网络,确保信号在传输线的始端和末端都能有效耦合。

- 控制信号线之间的间距,减少串扰。

- 采用屏蔽、地平面分割等手段降低电磁辐射和干扰。

- 进行仿真和实验测试,确保设计满足性能指标。

总结来说,信号完整性是高速电路设计的核心,理解和掌握相关知识对于数字硬件工程师至关重要,它关系到系统性能、可靠性和整体设计质量。通过深入学习和实践,工程师可以有效地应对高速数字电路带来的挑战,实现高效、稳定的电路设计。

178 浏览量

点击了解资源详情

点击了解资源详情

112 浏览量

480 浏览量

dajiangjin

- 粉丝: 0

- 资源: 1