掌握SystemVerilog三段式状态机设计 实现自动贩售机

需积分: 0 123 浏览量

更新于2024-08-05

收藏 402KB PDF 举报

实验四——自动贩售机的设计与实现1是一个旨在提升学生在IT领域特定技能的项目,其核心目标是让学生掌握有限状态机(Finite State Machine, FSM)的设计方法,并熟练应用SystemVerilog进行三段式状态机的建模。在这个实验中,学生将运用所学理论在硬件平台上,即远程FPGA云平台上,实践设计和实现一个模拟报纸自动贩售机的系统。

首先,实验的主要目标包括:

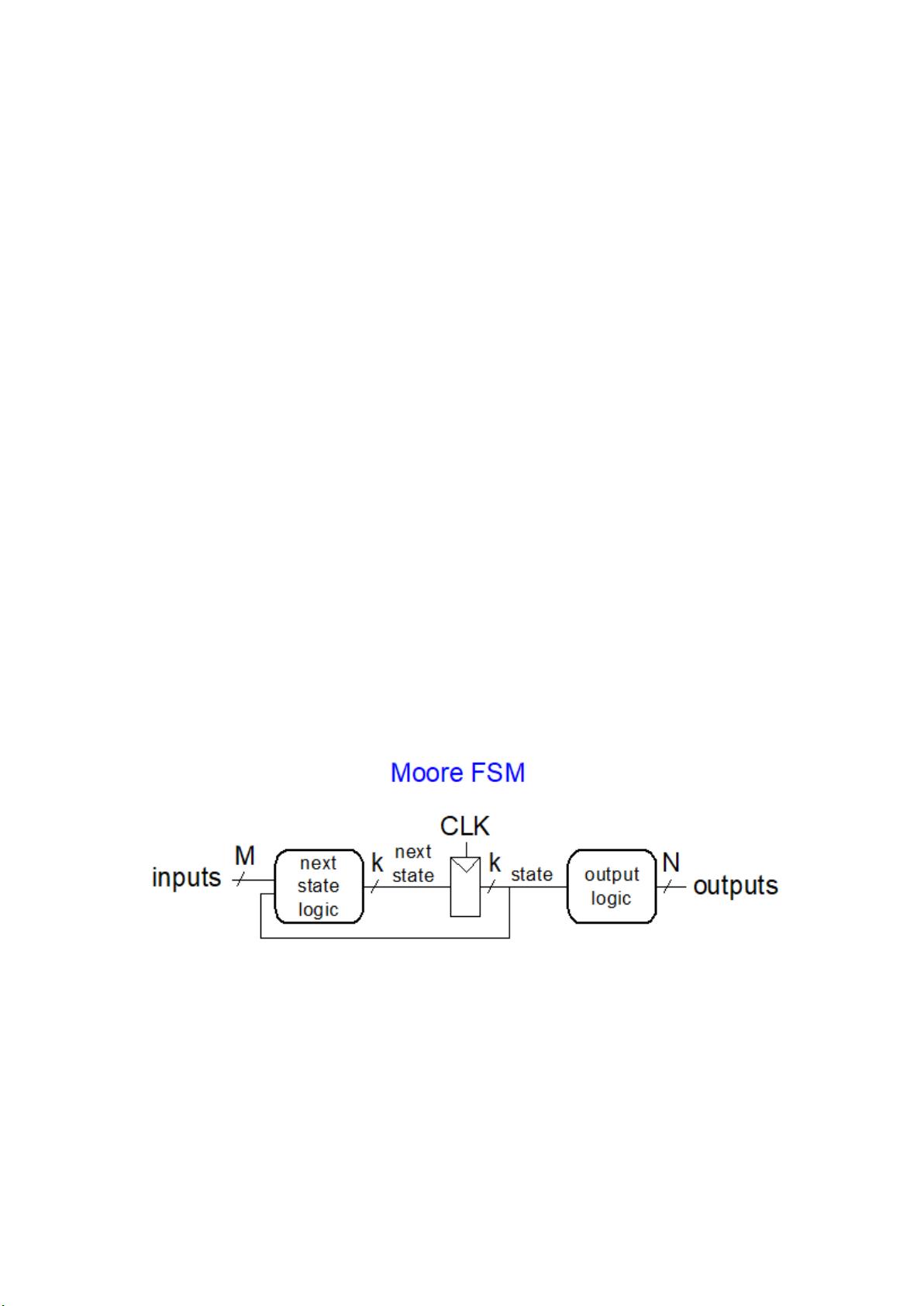

1. **有限状态机设计**:通过本实验,学生将深入理解Moore型和Mealy型状态机的区别,前者只依赖于当前状态决定输出,后者则同时考虑当前状态和输入。通过绘制状态转换图,学生会学习如何在设计中清晰地表达这两种类型的输出行为。

2. **SystemVerilog应用**:实验的核心技术是三段式状态机建模。它将状态机分为三个部分:第一段是同步时序逻辑,用于描述状态的转换,涉及状态寄存器的更新;第二段是组合逻辑,用于判断状态转移的条件;第三段是输出逻辑,根据状态决定器件的实际动作,可能是组合逻辑也可能是时序逻辑。这种划分有助于提高代码的可读性和效率。

实验环境中,学生需要熟悉的操作系统包括Windows 10和Ubuntu 16.04,以及Xilinx Vivado 2018.2作为开发工具。这些环境的选择确保了兼容性和高效性,尤其对于FPGA开发来说非常重要。

具体到实验内容,学生将设计一个包含四个七段数码管的报纸自动贩售机。顶层模块的设计图和输入/输出接口的详细描述将有助于构建系统的整体架构。实验过程中,学生需利用有限状态机模型控制机器的运作流程,例如识别货币投入、选择报纸类型、交易确认等操作。

在整个设计过程中,学生将面临挑战,如正确实现状态转移、处理实时输入、以及优化输出逻辑以满足实时性能需求。通过这个项目,他们将深化对硬件描述语言的理解,提高系统级设计和验证的能力,这对于未来在硬件工程师或嵌入式系统开发的职业道路上非常关键。

2022-07-03 上传

2022-05-29 上传

2022-12-08 上传

2021-01-14 上传

2022-04-06 上传

2020-05-30 上传