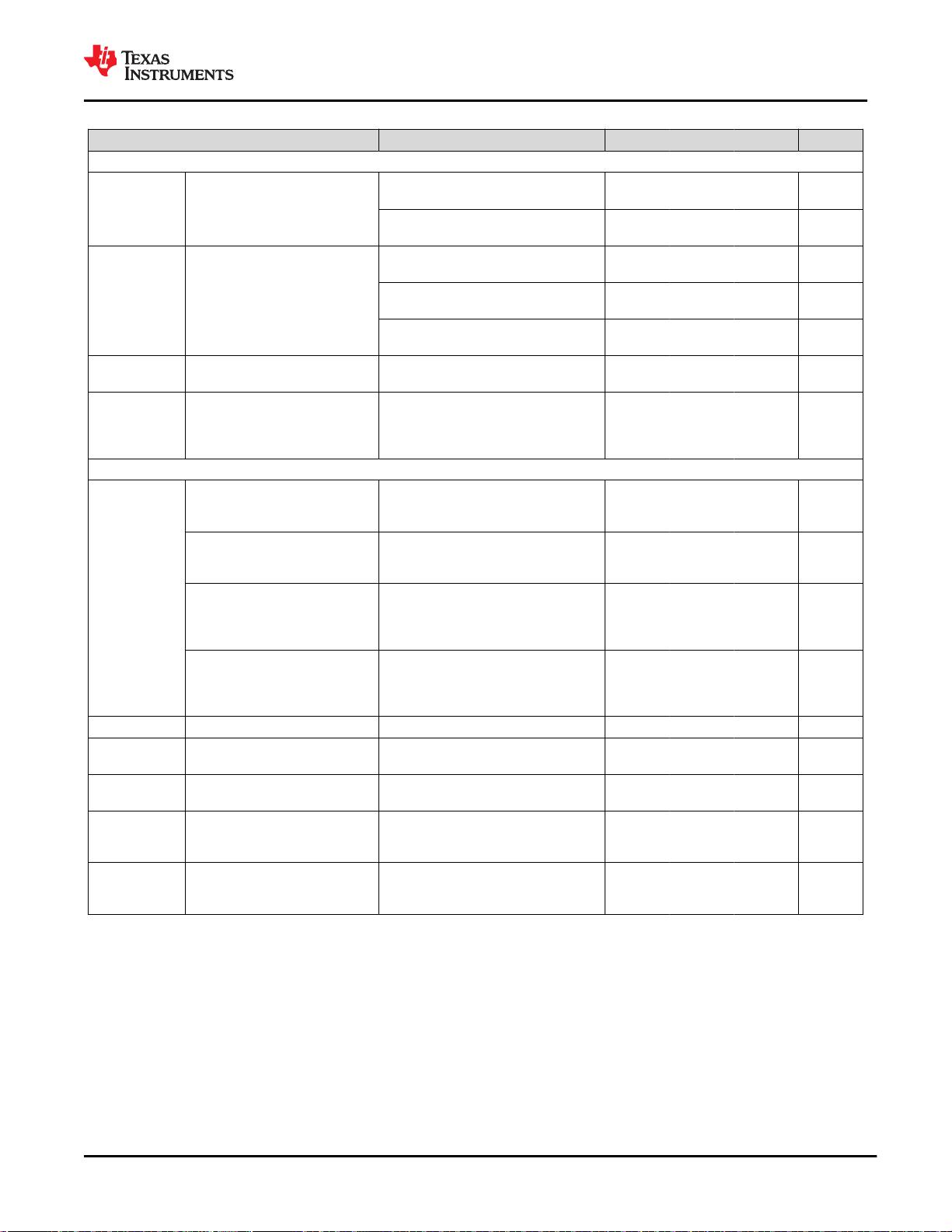

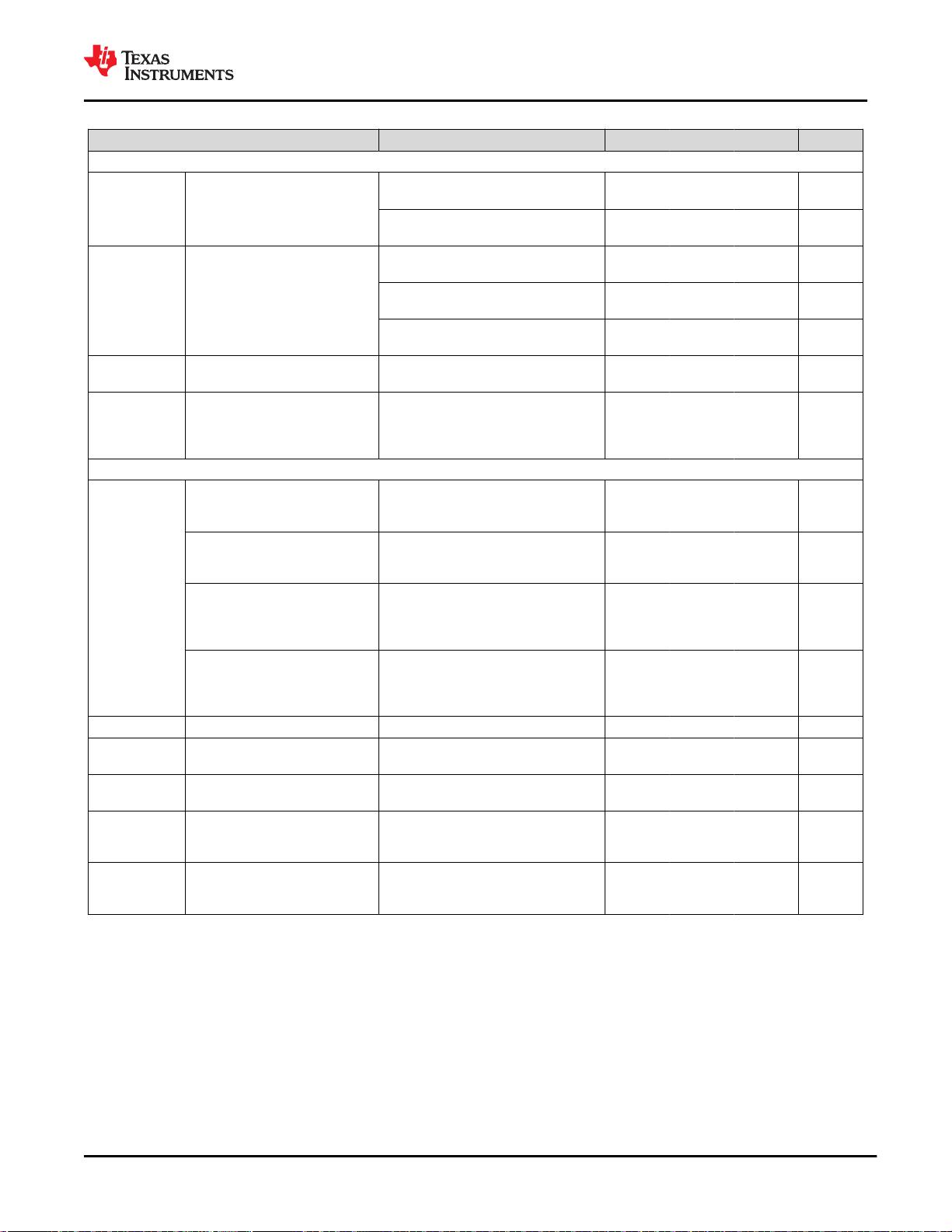

Over Recommended Operating Conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

POWER SUPPLY NOISE REJECTION (PSNR) / CROSSTALK SPURS

PSNR

50mV

Spur induced by power supply

noise (V

N

= 50 mVpp)

(6)

(7)

V

DD

= 3.3 V, V

DDO_x

= 3.3 V, 156.25

MHz, AC-DIFF output

–83

dBc

V

DD

= 3.3 V, V

DDO_x

= 3.3 V, 156.25

MHz, HCSL output

–78

dBc

PSNR

25mV

Spur induced by power supply

noise (V

N

= 25 mVpp)

(6)

(7)

V

DD

= 3.3 V, V

DDO_x

= 1.8 V, 156.25

MHz, AC-DIFF output

–63

dBc

V

DD

= 3.3 V, V

DDO_x

= 1.8 V, 156.25

MHz, HCSL output

–58

dBc

V

DD

= 3.3 V, V

DDO_x

= 1.8 V, 156.25

MHz, LVCMOS output

–45

dBc

SPUR

XTALK

Spur level due to output-to-output

crosstalk (adjacent channels)

(7)

f

OUTx

= 156.25 MHz, f

OUTy

= 155.52

MHz, AC-LVPECL

–75

dBc

SPUR

Highest spur level within 12 kHz

to 40 MHz band (excludes output

crosstalk and integer-boundary

spurs)

(7)

f

VCO1

= 2500 MHz, f

VCO2

= 6065.28

MHz, f

OUTx

= 156.25 MHz, f

OUTy

=

155.52 MHz, AC-LVPECL

–80

dBc

PLL CLOCK OUTPUT PERFORMANCE CHARACTERISTICS

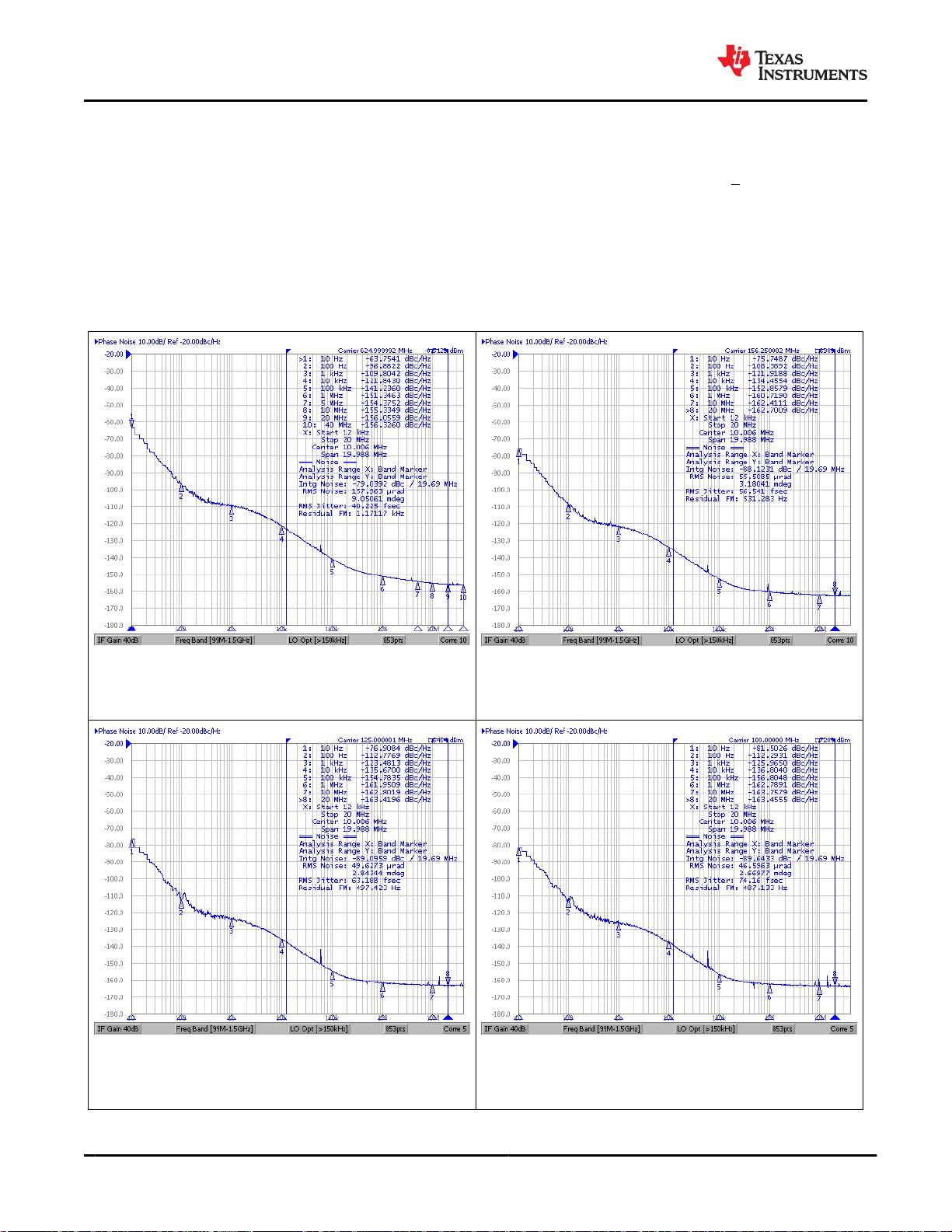

RJ

RMS Phase Jitter (12 kHz to 20

MHz)

(14)

312.5 MHz AC-LVPECL output from

APLL1, f

XO

= 48.0048 MHz, f

PD1

=

f

XO

/2, f

VCO1

= 2.5 GHz

50 80 fs RMS

RMS Phase Jitter (12 kHz to 20

MHz)

(14)

156.25 MHz AC-LVPECL output from

APLL1, f

XO

= 48.0048 MHz, f

PD1

=

f

XO

/2, f

VCO1

= 2.5 GHz

60 90 fs RMS

RMS Phase Jitter (12 kHz to 20

MHz)

(14)

153.6 MHz AC-LVPECL output from

APLL2, f

XO

= 48.0048 MHz, f

PD1

=

f

XO

/2, f

VCO1

= 2.5 GHz, f

PD2

= f

VCO1

/18,

f

VCO2

= 5.5296 GHz

125 200 fs RMS

RMS Phase Jitter (12 kHz to 20

MHz)

(14)

155.52 MHz AC-LVPECL output from

APLL2, f

XO

= 48.0048 MHz, f

PD1

=

f

XO

/2, f

VCO1

= 2.5 GHz, f

PD2

= f

VCO1

/18,

f

VCO2

= 5.59872 GHz

125 200 fs RMS

BW DPLL bandwidth range

(8)

Programmed bandwidth setting 0.01 4000 Hz

J

PK

DPLL closed-loop jitter

peaking

(10)

f

REF

= 25 MHz, f

OUT

= 10 MHz, DPLL

BW = 0.1 Hz or 10 Hz

0.1 dB

J

TOL

Jitter tolerance

Jitter modulation = 10 Hz, 25.78125

Gbps

6455 UI p-p

t

HITLESS

Phase hit between two reference

inputs with 0 ppm error

Valid for a single switchover event

between two clock inputs at the same

frequency

± 50 ps

f

HITLESS

Frequency transient during hitless

switch

Valid for a single switchover event

between two clock inputs at the same

frequency

± 10 ppb

(1) Total device current can be estimated by summing the individual IDD_x and IDDO_x per pin for all blocks enabled in a

given configuration.

(2) Configuration A (All PLL blocks on except APLL2 is disabled): f

REF

= 25 MHz, f

XO

= 48.0048 MHz, f

VCO1

= 2.5 GHz.

(3) IDDO_x current for an operating output is the sum of mux, divider, and an output format.

(4) For a differential input clock below 5 MHz, TI recommends to disable the differential input amplitude monitor and enable at least one

other monitor (frequency, window detectors) to validate the input clock. Otherwise, consider using an LVCMOS clock for an input

below 5 MHz.

(5) An output frequency over f

OUT

max spec is possible, but output swing may be less than V

OD

min specification.

(6) PSNR is the single-sideband spur level (in dBc) measured when sinusoidal noise with amplitude V

N

and frequency f

N

(between 100

kHz and 1 MHz) is injected onto VDD and VDDO_x pins.

(7) DJ

SPUR

(ps pk-pk) = [2 × 10

(dBc/20)

/ (π × f

OUT

) × 1E6], where dBc is the PSNR or SPUR level (in dBc) and f

OUT

is the output frequency

(in MHz).

(8) Actual loop bandwidth may be lower. The valid loop bandwidth range may be constrained by the DPLL TDC frequency used in a given

configuration.

www.ti.com.cn

LMK5B12204

ZHCSLM0A – MAY 2020 – REVISED JANUARY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

15

Product Folder Links: LMK5B12204