- 18 -

KMR820001M-B609 MCP Memory

Rev. 1.0

datasheet

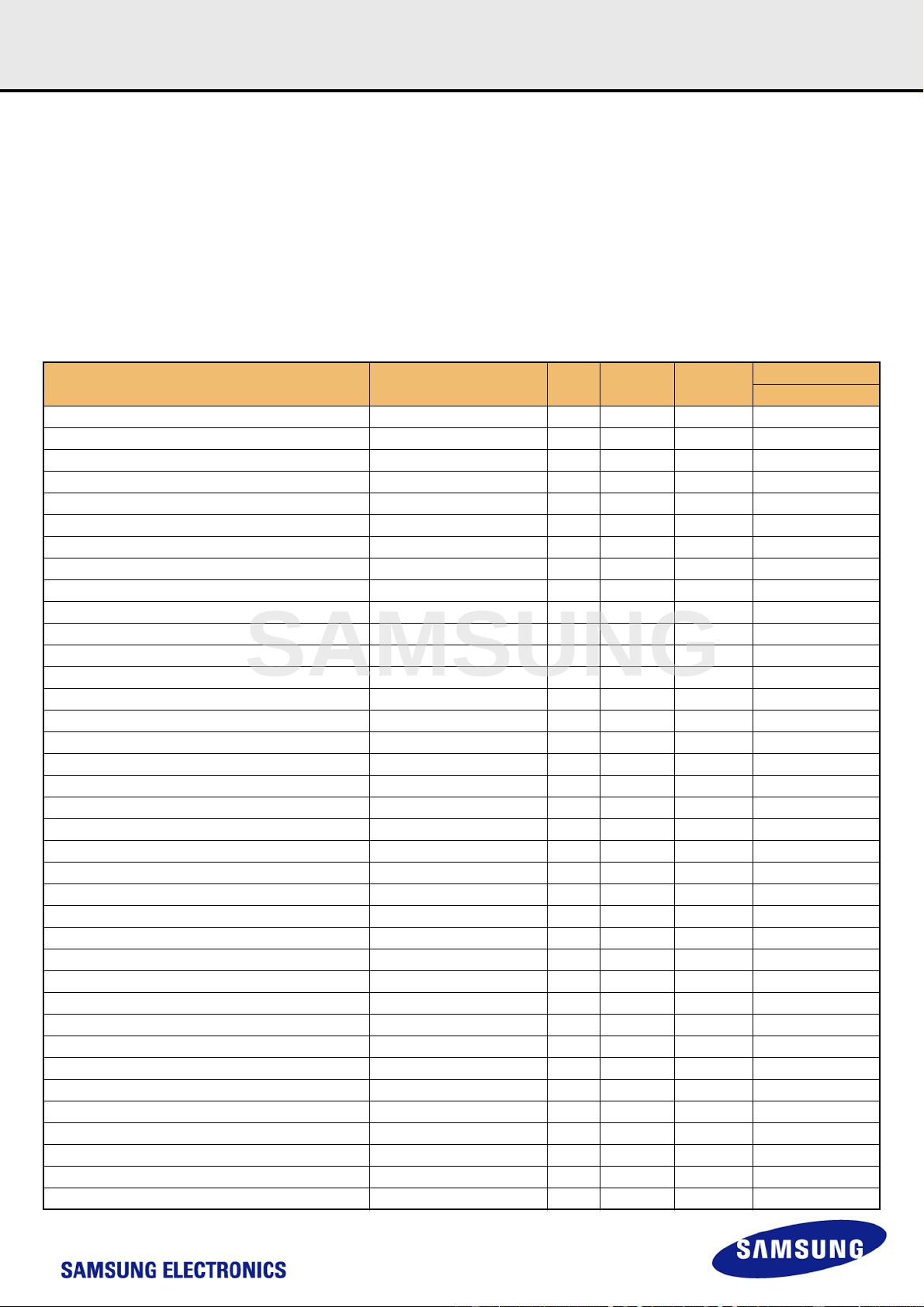

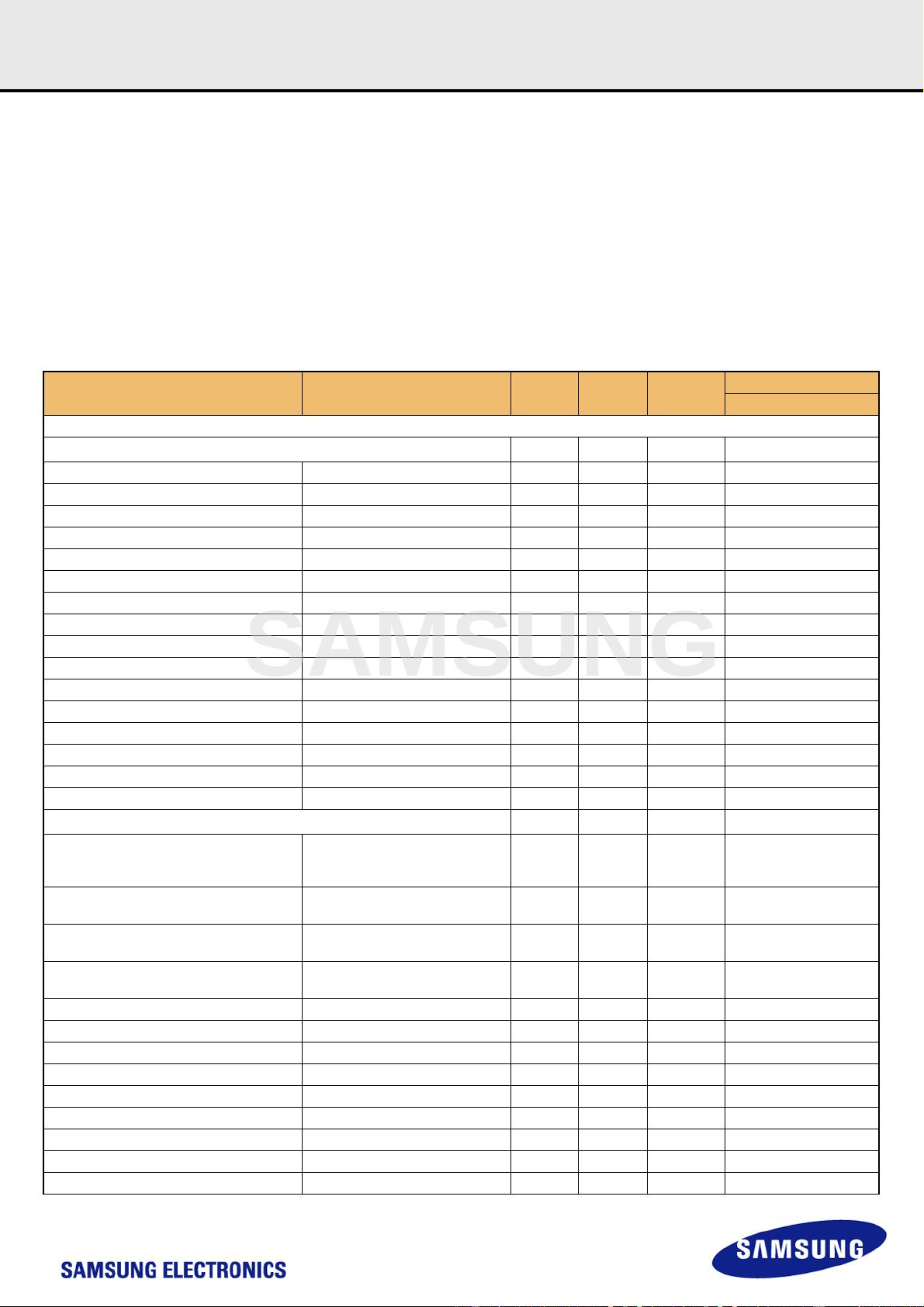

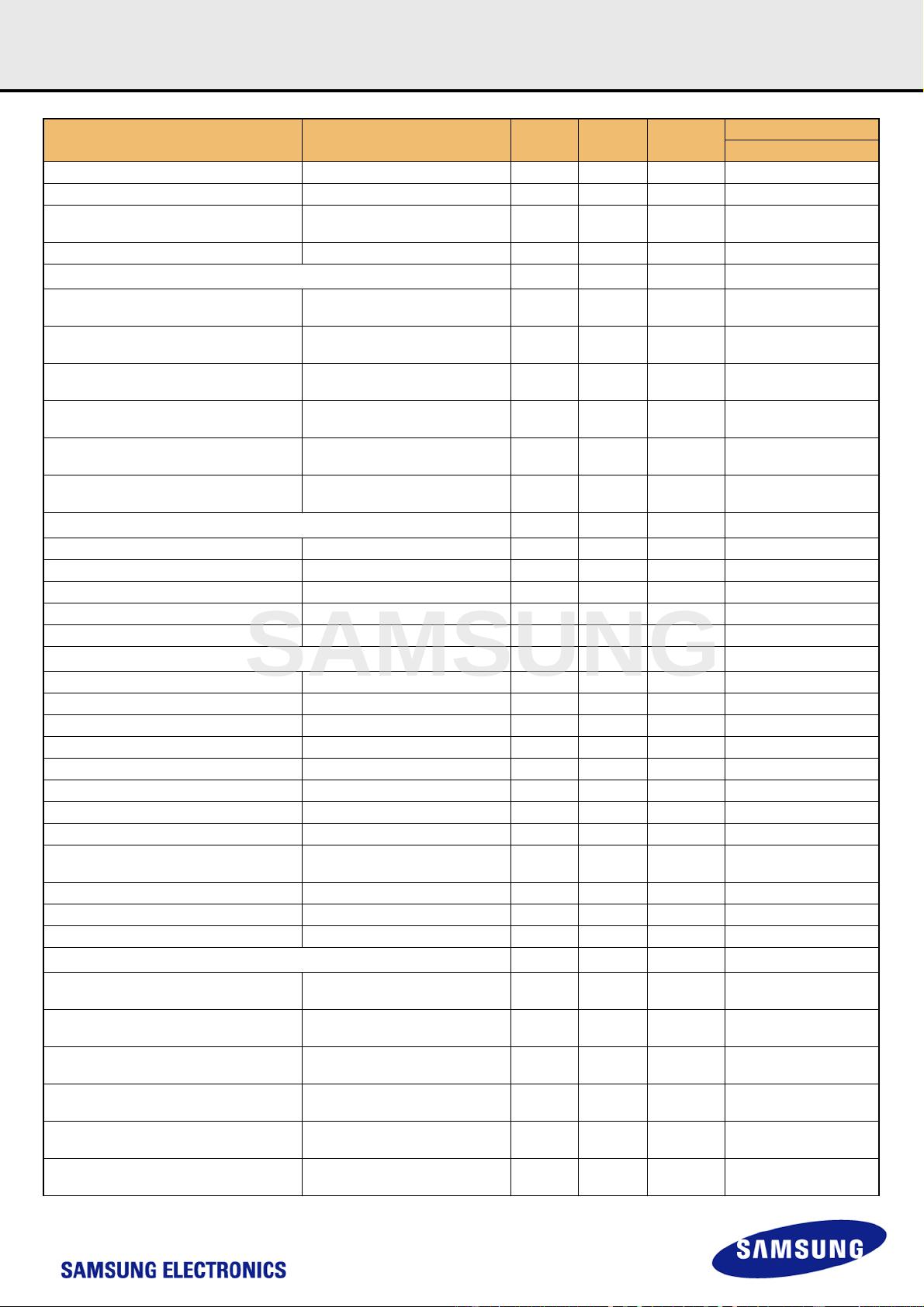

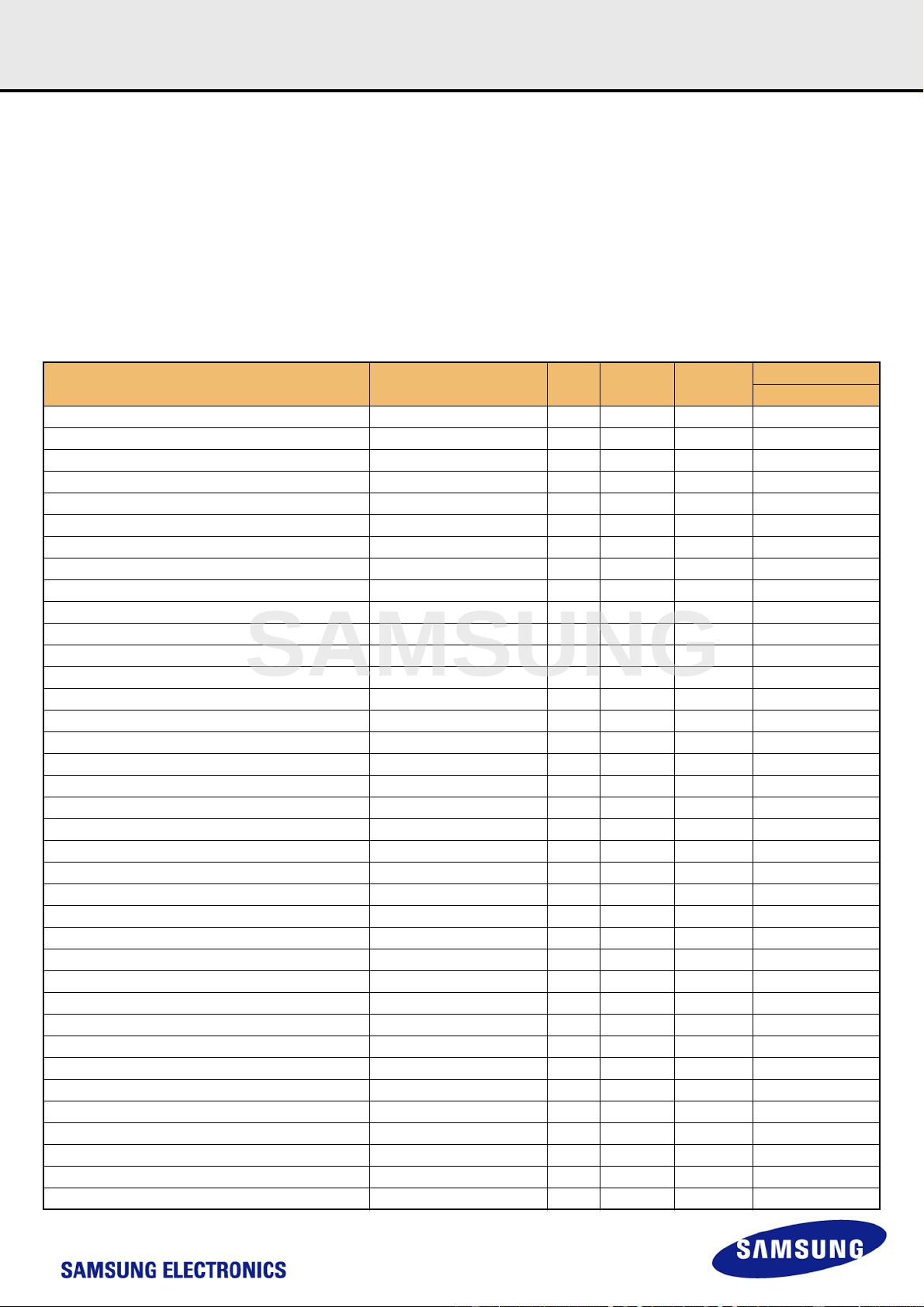

4.3 CSD Register

The Card-Specific Data register provides information on how to access the e·MMC contents. The CSD defines the data format, error correction type, max-

imum data access time, data transfer speed, whether the DSR register can be used etc. The programmable part of the register (entries marked by W or

E, see below) can be changed by CMD27. The type of the entries in the table below is coded as follows:

R : Read only

W: One time programmable and not readable.

R/W: One time programmable and readable.

W/E : Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and not readable.

R/W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and readable.

R/W/C_P: Writable after value cleared by power failure and HW/ rest assertion (the value not cleared by CMD0 reset) and readable.

R/W/E_P: Multiple writable with value reset after power failure, H/W reset assertion and any CMD0 reset and readable.

W/E/_P: Multiple wtitable with value reset after power failure, H/W reset assertion and any CMD0 reset and not readable.

[Table 17] CSD Register

Name Field Width Cell Type CSD-slice

CSD Value

16 GB

CSD structure CSD_STRUCTURE 2 R [127:126] 0x03

System specification version SPEC_VERS 4 R [125:122] 0x04

Reserved - 2 R [121:120] -

Data read access-time 1 TAAC 8 R [119:112] 0x27

Data read access-time 2 in CLK cycles (NSAC*100) NSAC 8 R [111:104] 0x01

Max. bus clock frequency TRAN_SPEED 8 R [103:96] 0x32

Device command classes CCC 12 R [95:84] 0xF5

Max. read data block length READ_BL_LEN 4 R [83:80] 0x09

Partial blocks for read allowed READ_BL_PARTIAL 1 R [79:79] 0x00

Write block misalignment WRITE_BLK_MISALIGN 1 R [78:78] 0x00

Read block misalignment READ_BLK_MISALIGN 1 R [77:77] 0x00

DSR implemented DSR_IMP 1 R [76:76] 0x00

Reserved - 2 R [75:74] -

Device size C_SIZE 12 R [73:62] 0xFFF

Max. read current @ VDD min VDD_R_CURR_MIN 3 R [61:59] 0x06

Max. read current @ VDD max VDD_R_CURR_MAX 3 R [58:56] 0x06

Max. write current @ VDD min VDD_W_CURR_MIN 3 R [55:53] 0x06

Max. write current @ VDD max VDD_W_CURR_MAX 3 R [52:50] 0x06

Device size multiplier C_SIZE_MULT 3 R [49:47] 0x07

Erase group size ERASE_GRP_SIZE 5 R [46:42] 0x1F

Erase group size multiplier ERASE_GRP_MULT 5 R [41:37] 0x1F

Write protect group size WP_GRP_SIZE 5 R [36:32] 0x0F

Write protect group enable WP_GRP_ENABLE 1 R [31:31] 0x01

Manufacturer default ECC DEFAULT_ECC 2 R [30:29] 0x00

Write speed factor R2W_FACTOR 3 R [28:26] 0x04

Max. write data block length WRITE_BL_LEN 4 R [25:22] 0x09

Partial blocks for write allowed WRITE_BL_PARTIAL 1 R [21:21] 0x00

Reserved - 4 R [20:17] -

Content protection application CONTENT_PROT_APP 1 R [16:16] 0x00

File format group FILE_FORMAT_GRP 1 R/W [15:15] 0x00

Copy flag (OTP) COPY 1 R/W [14:14] 0x01

Permanent write protection PERM_WRITE_PROTECT 1 R/W [13:13] 0x00

Temporary write protection TMP_WRITE_PROTECT 1 R/W/E [12:12] 0x00

File format FILE_FORMAT 2 R/W [11:10] 0x00

ECC code ECC 2 R/W/E [9:8] 0x00

CRC CRC 7 R/W/E [7:1] -

Not used, always’1’ - 1 — [0:0] -