电源完整性设计详解:噪声问题与解决策略

需积分: 0 139 浏览量

更新于2024-07-26

收藏 285KB PDF 举报

“电源完整性设计详解,开关电源原理及设计!为电子爱好者提供资料!”

电源完整性设计是电子设计中的一个重要领域,它关注的是确保电子设备的电源系统能够提供纯净、稳定的电压供应,以保证整个系统运行的可靠性和性能。电源完整性涉及到电源噪声的管理和抑制,因为电源噪声可以对电路性能产生严重影响,包括信号质量下降、电磁干扰增加以及系统稳定性降低。

1、为什么要重视电源噪声问题?

电源噪声问题不容忽视,因为在现代集成电路中,芯片内部的晶体管数量巨大。这些晶体管共享同一电源引脚,当晶体管状态转换时,会导致电源电压波动,即电源噪声。这种噪声如果传播到其他还在转换状态的晶体管,可能会导致逻辑错误,特别是在时序敏感的电路中,噪声可能导致信号误触发,从而影响整个系统的工作。

2、电源系统噪声余量分析:

电源系统需要有足够的噪声余量,以应对内部和外部的噪声源。噪声余量是指电源电压能够承受的噪声幅度,而不影响电路的正常工作。分析噪声余量有助于确定系统设计的安全阈值和优化去耦策略。

3、电源噪声的产生:

电源噪声主要来源于两个方面:一是内部噪声,由于晶体管开关活动引起的;二是外部噪声,例如来自电源线的传导噪声和辐射噪声。

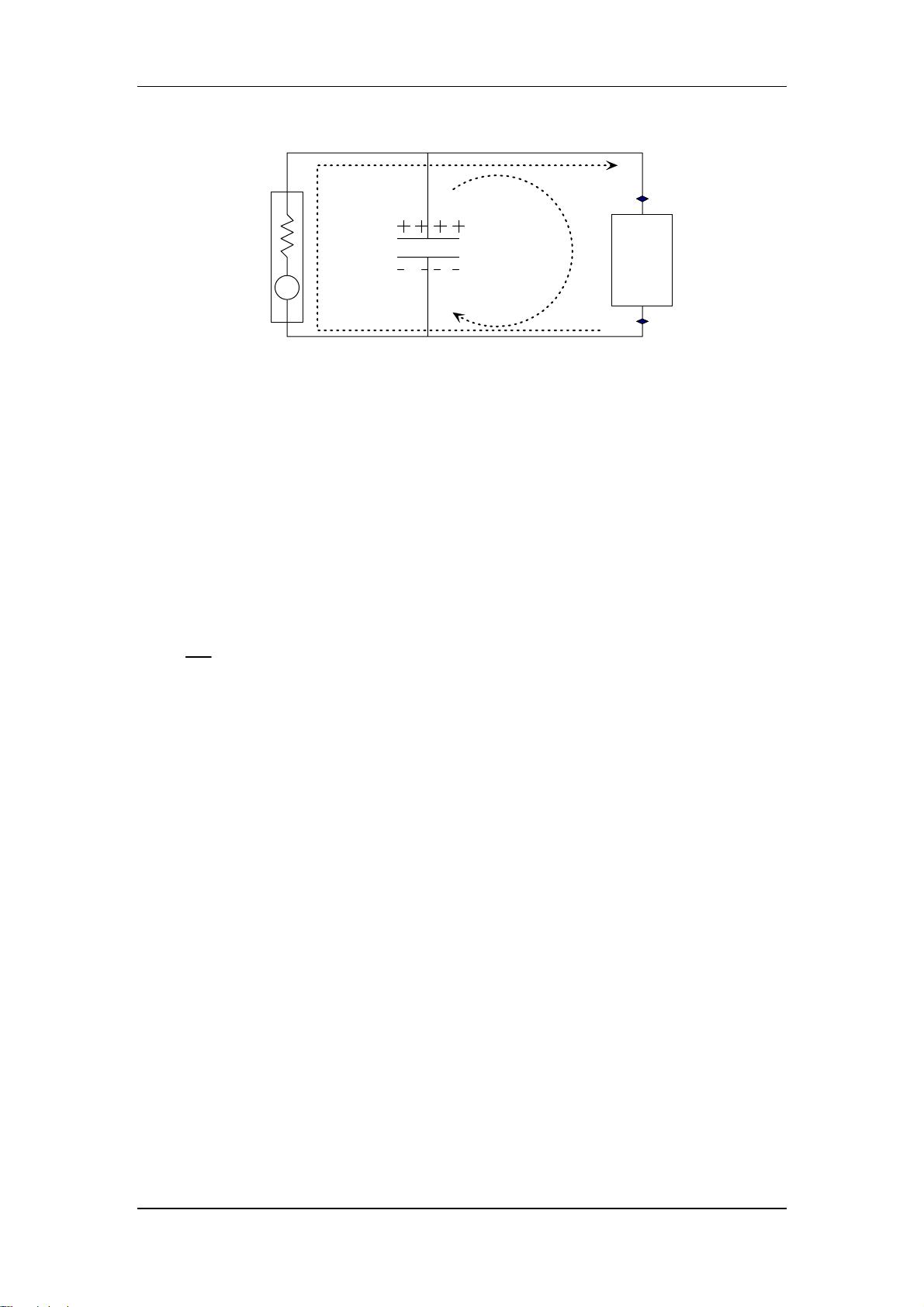

4、电容退耦:

电容退耦是抑制电源噪声的关键手段。退耦电容可以看作是能量存储装置,当电源需求增加时提供瞬时电流,减少电压波动。同时,电容也可视为一个阻抗元件,通过匹配电源阻抗和负载阻抗,降低噪声传播。

5、实际电容的特性:

实际电容并非理想的纯电容,它们具有等效串联电阻(ESR)和等效串联电感(ESL),这些因素会影响电容的滤波效果和谐振行为。

6、电容的安装谐振频率:

电容与PCB走线、封装电感等构成的系统会产生谐振,其频率取决于电容值、ESL和走线特性。设计时需避免电容工作在谐振点,以免放大噪声。

7、局部去耦设计方法:

局部去耦是指在每个关键负载附近放置电容,以减少电源路径的阻抗,提高瞬态响应。目标阻抗(Target Impedance)的概念用于指导电容布局,以保证在所需频段内电源阻抗最小。

8、电源系统的去耦设计:

去耦设计需要考虑电容量的选择、电容并联的反谐振效应、ESR的影响以及电容的去耦半径等因素。合理选择电容组合能有效抑制噪声,而正确的安装方法则可以避免谐振增强噪声。

9、结束语:

电源完整性设计是确保电子设备稳定运行的关键,需要深入理解电源噪声的产生机制,掌握有效的去耦策略,以优化电源系统的性能。

以上内容摘自于争博士的《电源完整性设计详解》,详细阐述了电源完整性设计的重要性,电源噪声的来源,以及如何通过电容退耦等方法来改善电源系统性能。对于电子爱好者和工程师来说,这份资料提供了宝贵的理论知识和实践经验。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-04-06 上传

2010-10-27 上传

2012-05-12 上传

2013-04-21 上传

2011-12-23 上传

2023-07-27 上传

zbh2012

- 粉丝: 4

- 资源: 9

最新资源

- 3088㎡三层框架图书馆钢筋及广联达算量(含CAD图纸).rar

- Adafruit_PlatformDetect-3.45.2-py3-none-any.whl.zip

- spray-dots:我们探索随着点而移动的绘画事物

- MATLAB数据字典生成代码-dsc-0-03-03-introducing-python-libraries-nyc-career-ds-0

- EliteParkingXamarin:使用 Xamarin 和 AngularJS 开发 EliteParking 混合移动应用程序

- 智能家居控制app ui .sketch素材下载

- 3091.17平米住宅楼施组及施工图预算(工程量计算、施组、平面图、进度表).rar

- 小程序源码 samsung 蓝牙4.0开发工具包和BLE例子.rar

- Adafruit_BNO055-1.0.1-py2-none-any.whl.zip

- kaiti_GB2312.zip

- 房建工程施工组织设计-某办公楼室内外装饰施工组织设计方案

- MATLAB数据字典生成代码-dsc-0-03-03-introducing-python-libraries-online-ds-pt-03

- Musichspeler:基于网络的音频播放器-开源

- sinx的matlab代码-matlab-engineering-codes:这将是关于在matlab上解决工程问题

- 海洋环保公益组织企业网站html静态模板.zip

- 3116.88平方,六层框架办公楼(计算书、建筑、结构施工图).rar