倒装芯片RDL布线技术:拥挤难题与优化策略

179 浏览量

更新于2024-09-02

收藏 341KB PDF 举报

在现代电子设计中,倒装芯片的布线层电路板布线技术是一项关键要素。由于倒装芯片(Flip Chip Ball Grid Array, FCBGA)的特点,其I/O需求通常远超传统的线绑定封装,这促使工程师采用更高效的解决方案来处理大规模、高密度的I/O连接。在布线层设计中,重新布线层(RDL)扮演了至关重要的角色,它作为一个额外的金属层,位于芯片与封装之间,负责将裸片的I/O焊盘与凸点焊盘进行连接。

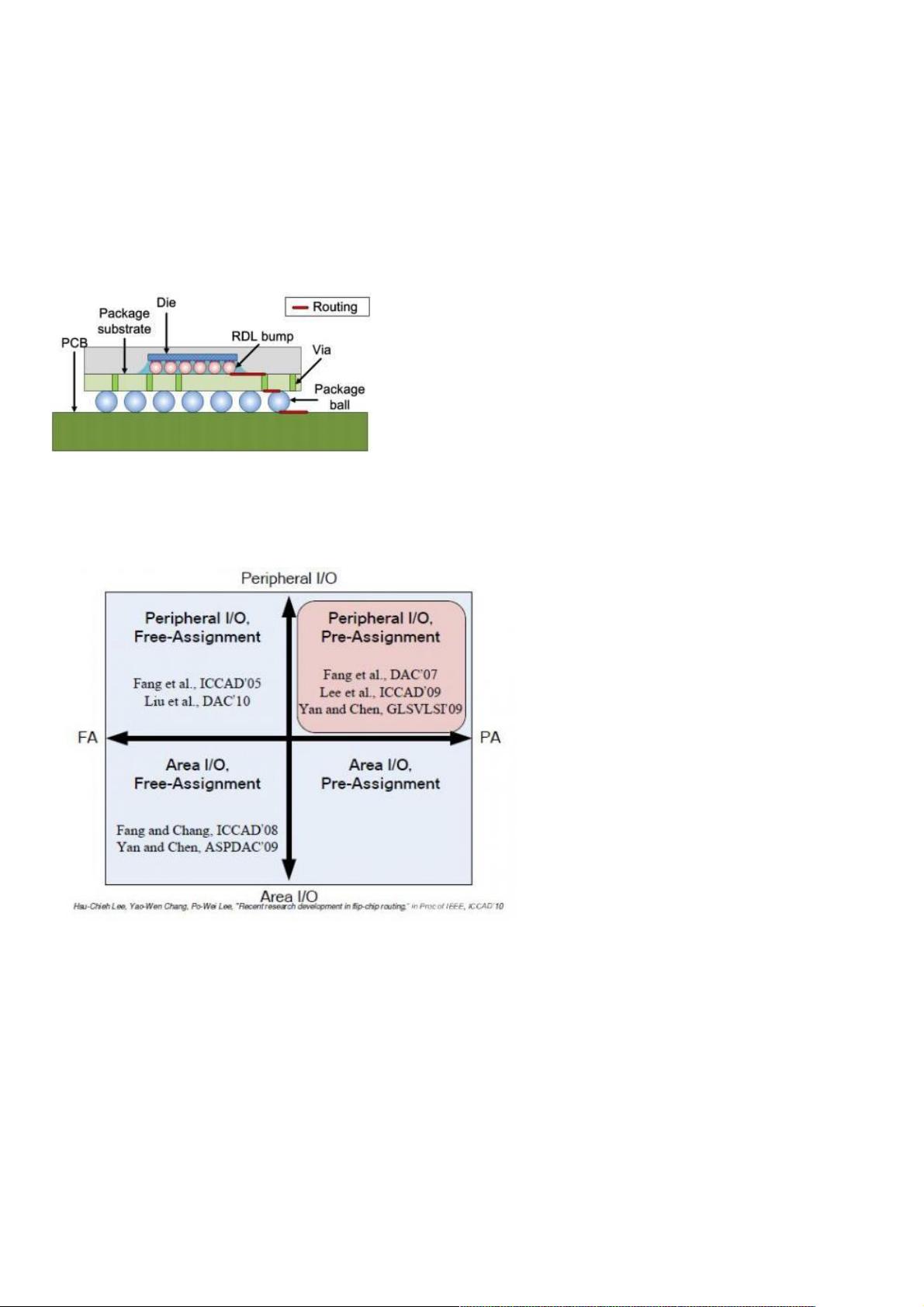

在非最优化的I/O凸点分配策略下,比如自由分配(Free Allocation, FA)和预分配(Pre-Allocation, PA),电路板可能会变得极其拥挤。FA允许每个I/O焊盘灵活选择凸点,但这增加了布线复杂性,因为分配和布线需要同时考虑。相比之下,PA方法虽然简化了交叉连接问题,但预分配问题的解决更为困难,不过对设计师而言,它提供了更好的控制和可预测性。

图1展示了倒装芯片的结构,信号线通过包括RDL在内的多个层面传输,以优化信号路径和减小电感,这对于高速信号的传输至关重要。AI/O(Area I/O)和PI/O(Peripheral I/O)是两种常见的倒装芯片结构,前者将I/O集中在芯片的特定区域,后者则将I/O分布在芯片边缘,每种结构都有其独特的挑战和优势。

设计时需要权衡各种因素,如信号完整性、散热效率和生产成本,以确保最佳的性能和制造可行性。对于大型倒装芯片项目,可能需要结合自动化工具和专家经验来优化I/O凸点分配,以提升布线效率和电路板的整体性能。倒装芯片的布线层电路板设计是一项精细且技术密集的工作,它直接影响到芯片的性能表现和整体系统效能。

2023-07-23 上传

2021-09-25 上传

2023-07-13 上传

2023-07-27 上传

2023-05-13 上传

2023-04-30 上传

2023-06-07 上传

2023-07-24 上传

2023-03-25 上传

weixin_38717574

- 粉丝: 14

- 资源: 925

最新资源

- 高效办公必备:可易文件夹批量生成器

- 吉林大学图形学与人机交互课程作业解析

- 8086与8255打造简易乒乓球游戏机教程

- Win10下C++开发工具包:Bongo Cat Mver、GLEW、GLFW

- Bootstrap前端开发:六页果蔬展示页面

- MacOS兼容版VSCode 1.85.1:最后支持10.13.x版本

- 掌握cpp2uml工具及其使用方法指南

- C51单片机星形流水灯设计与Proteus仿真教程

- 深度远程启动管理器使用教程与工具包

- SAAS云建站平台,一台服务器支持数万独立网站

- Java开发的博客API系统:完整功能与接口文档

- 掌握SecureCRT:打造高效SSH超级终端

- JAVA飞机大战游戏实现与源码分享

- SSM框架开发的在线考试系统设计与实现

- MEMS捷联惯导解算与MATLAB仿真指南

- Java实现的学生考试系统开发实战教程