Verilator与Gtwave整合仿真教程:从入门到实践

需积分: 0 86 浏览量

更新于2024-08-05

1

收藏 300KB PDF 举报

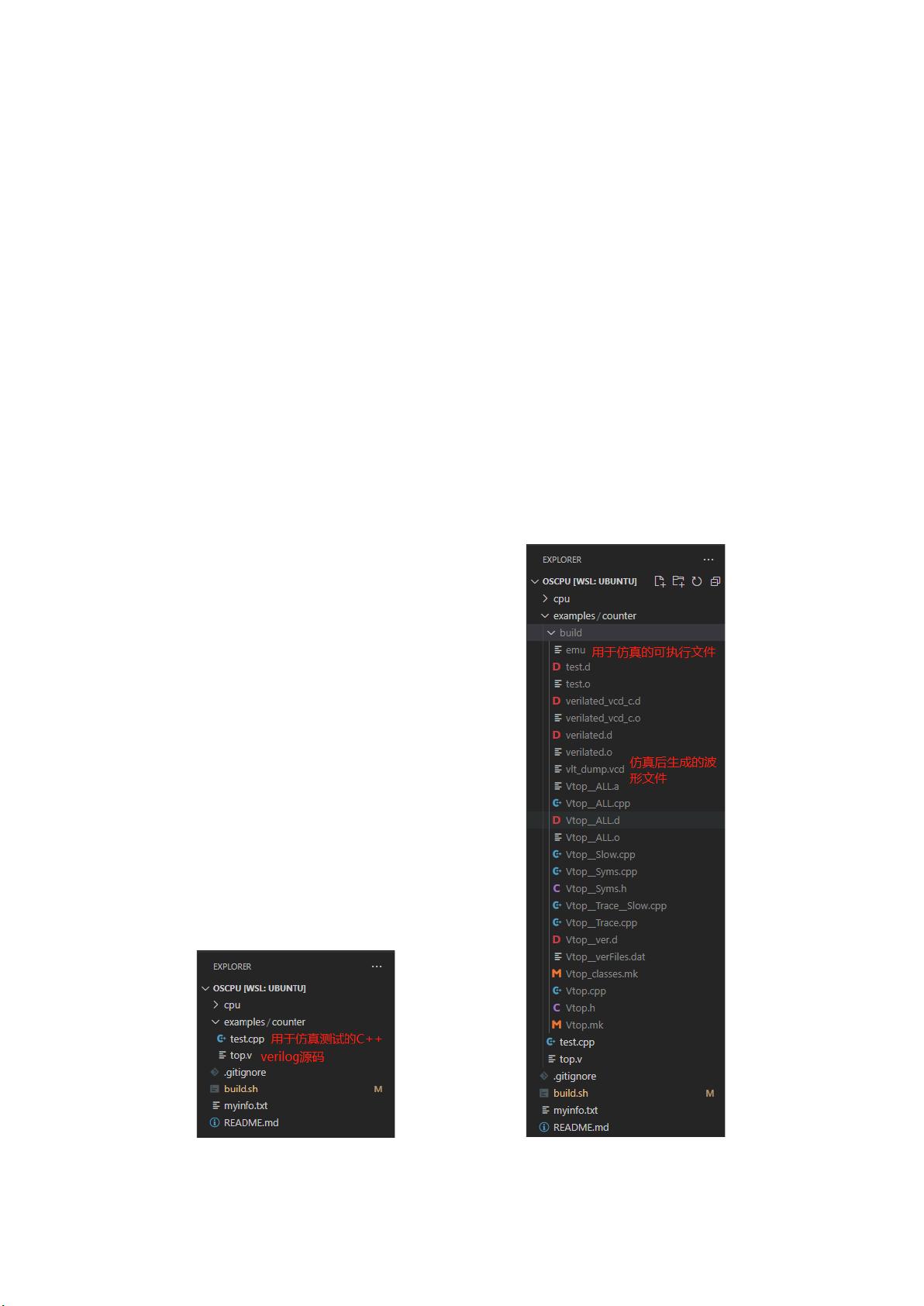

"这篇教程介绍了如何使用Verilator和Gtkwave进行快速上手实践,主要针对RISC-V相关的Verilog设计。Verilator是一个工具,能够将Verilog和SystemVerilog硬件描述语言转换为C++或SystemC模型,便于进行仿真。而Gtkwave则用于显示仿真产生的波形数据,帮助开发者分析设计行为。教程涵盖了工程文件结构、Verilog顶层文件编写、应用程序代码编辑以及Verilator和Gtkwave的安装与使用。"

在Verilog设计中,`$(top).v`是顶层模块文件,它定义了模块的内部逻辑并暴露必要的输入/输出(IO)信号。开发者需要在这个文件中实现模块的功能,并确保对外部世界提供接口。例如,一个简单的`clock`信号可能会在此处声明,以便其他部分的代码可以与其交互。

应用程序代码通常存在于独立的C++测试文件中,如`$(test).cpp`。在这个文件中,开发者会包含由Verilator生成的头文件`V$(top).h`。这允许C++代码直接实例化`V$(top)`类,进而访问和操作Verilog模块的IO端口。`V$(top)`类封装了所有可读写的IO信号,它们作为成员变量,使用户可以模拟时钟和其他信号的变化。例如,通过设置`clock`端口的值为0和1,并调用`eval()`方法,可以模拟一个完整的时钟周期。

在实际操作中,环境通常为Linux(如Ubuntu 20.04),使用虚拟机软件如VMware Workstation 15 Pro或Oracle VM VirtualBox。教程推荐避免使用`apt install verilator`来安装,因为这可能得到较旧的版本。推荐使用从特定网站下载的自动化脚本安装最新版的Verilator,以确保获得最佳功能和性能。

安装Verilator后,开发者可以利用它编译Verilog代码,并生成C++模拟器。Gtkwave的安装和使用则让开发者能够查看和分析仿真过程中产生的波形数据,这对于调试和验证设计行为至关重要。通过将Verilator生成的波形文件加载到Gtwave中,可以清晰地看到信号随时间的变化,从而更有效地理解设计的工作原理。

这个教程为RISC-V开发者提供了一个基础的Verilator和Gtkwave使用指南,帮助他们快速入门硬件描述语言的仿真和验证过程。通过学习这个教程,开发者可以掌握如何构建和测试Verilog模块,以及如何利用可视化工具分析其行为,这对于任何硬件设计项目都是至关重要的。

点击了解资源详情

点击了解资源详情

246 浏览量

798 浏览量

点击了解资源详情

2011-05-22 上传

342 浏览量

246 浏览量

2022-05-17 上传

天使的梦魇

- 粉丝: 39

- 资源: 321

最新资源

- easypanel虚拟主机控制面板 v1.3.2

- Coursera

- wind-js-server:用于将Grib2风向预报数据公开为JSON的服务

- 生命源头论坛 LifeYT-BBS V2.1

- TUTK_IOTC_Platform_14W42P2.zip TUTK IOTC官方sdk

- WeatherJournalApp

- 电商小程序源码项目实战

- 美女婚纱照片模板下载

- GB 50231-1998 机械设备安装工程施工及验收通用规范.rar

- MPT-开源

- facebook-archive:使用Facebook的存档数据可以享受一些乐趣

- 阿普奇工业显示器PANEL2000.zip

- action_react

- Torus-开源

- 应用js

- WPF将控件中的文字旋转.zip