北大微电子学Verilog全攻略:从入门到高级仿真与综合

需积分: 46 144 浏览量

更新于2024-07-23

收藏 2.01MB PDF 举报

本篇北大微电子学Verilog超详细教程深入讲解了数字集成电路设计的基础知识,由北大微电子学系的于敦山教授主讲。课程分为五个主要部分:

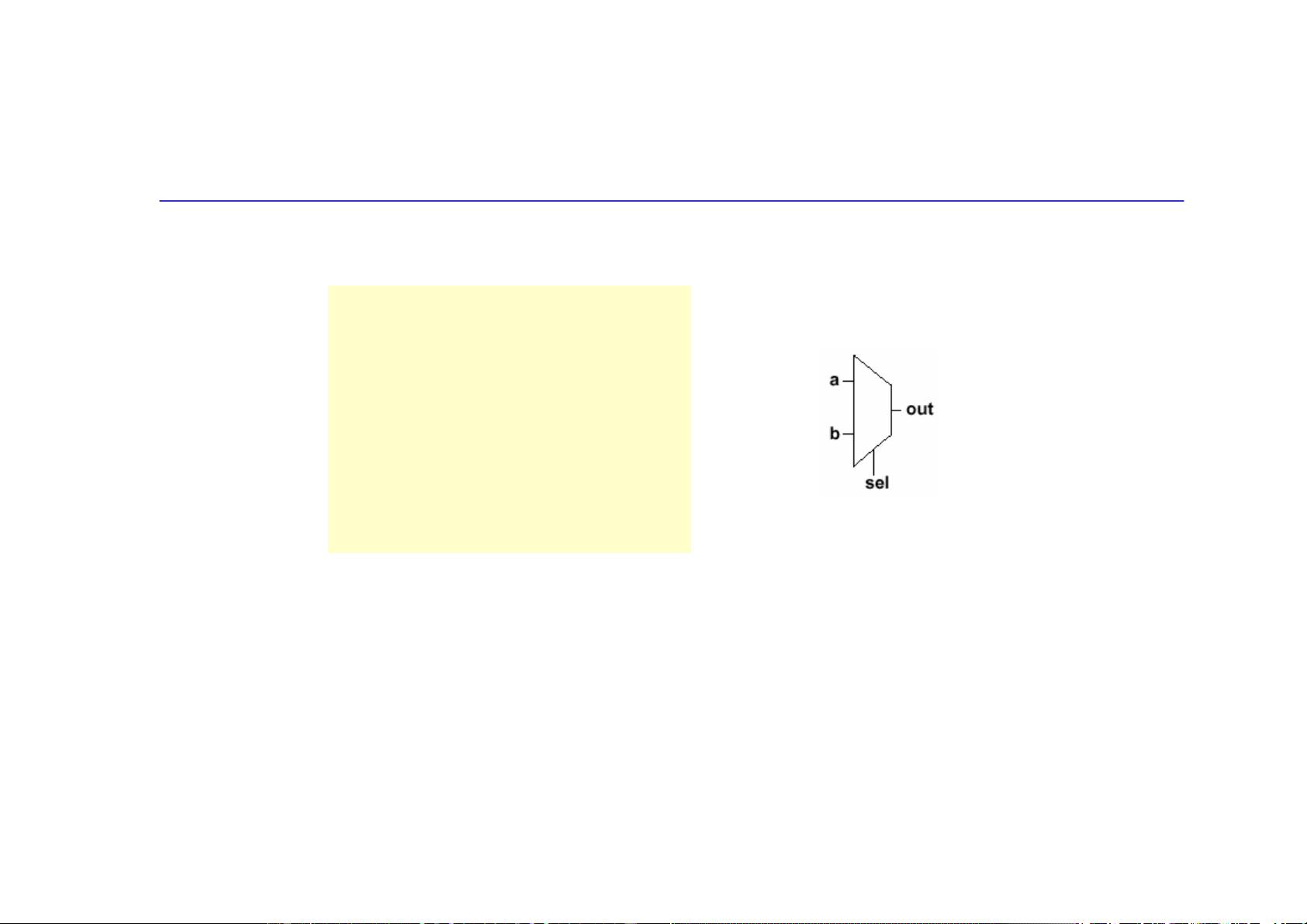

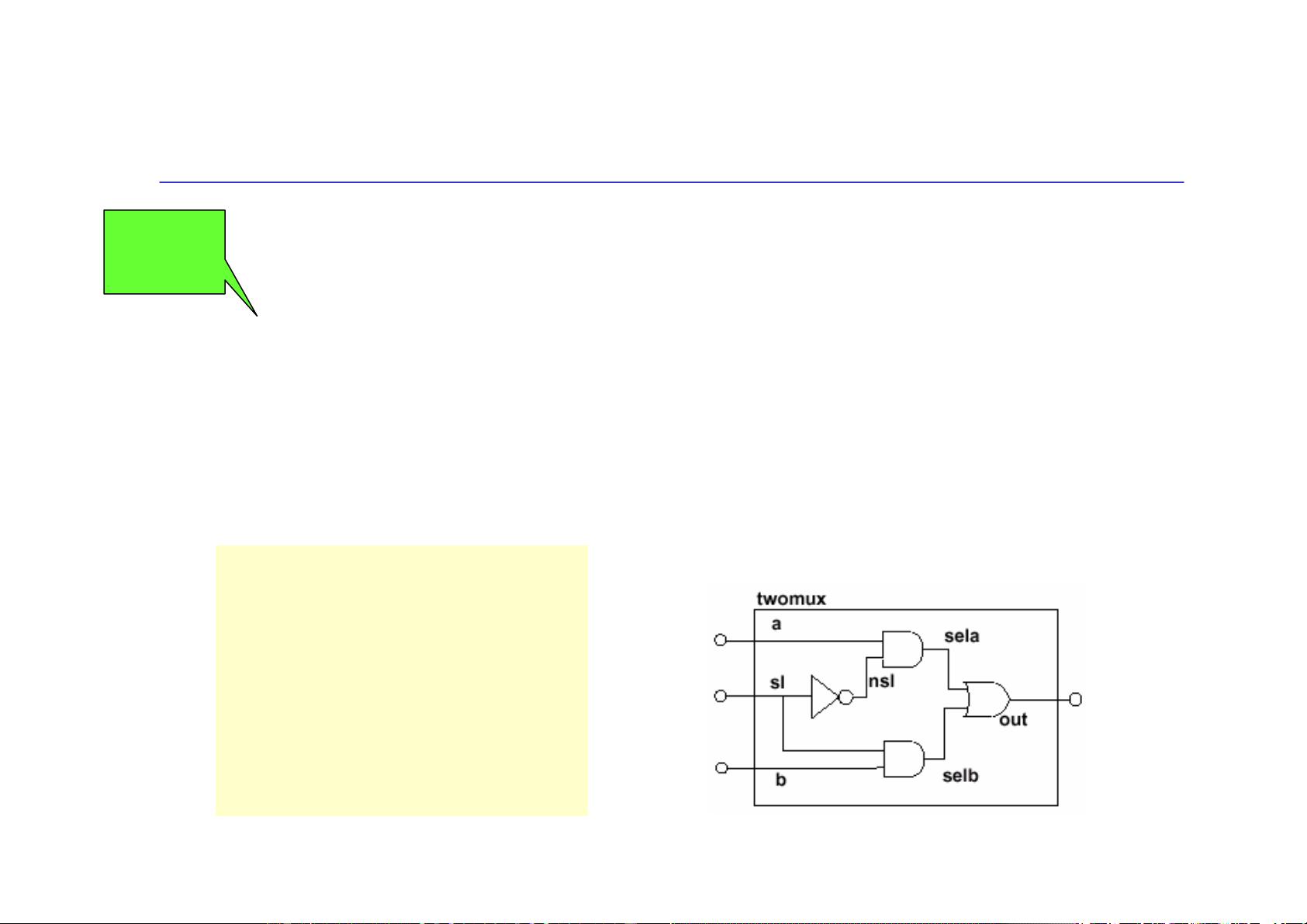

1. **Verilog HDL入门**:首先介绍Verilog Hardware Description Language (HDL),涵盖了Verilog的应用、语言构成元素(如结构级描述、行为级描述、任务task和函数function)、延时特性和测试平台(testbench)的构建。教授讲解了如何利用Verilog进行激励与控制以及结果验证。

2. **Cadence Verilog仿真器**:深入讲解了Cadence工具在Verilog设计中的应用,包括设计编译、仿真过程、源库的使用、调试技巧(命令行和图形用户界面)、延时处理以及性能仿真。此外,还介绍了如何利用NCVerilog进行设计环境管理和周期仿真。

3. **逻辑综合**:涉及静态时序分析(STA)、Design Analyzer环境以及可综合的HDL编码规范,讨论了Verilog中的一些实用技巧,如Designware库的利用和综合划分策略。

4. **设计约束和优化**:这部分介绍了设计环境的设置、设计约束的设置方法,以及如何进行设计编译和状态机(FSM)的优化。实验环节涉及到设计报告的生成和分析。

5. **自动布局布线工具**:简要介绍了Silicon Ensemble这种自动布局布线工具,帮助学生理解设计流程中此环节的重要性。

整个课程共计54学时,分为讲座、实验和考试三个部分。参考书目列出了几本权威教材,如Cadence官方文档、《硬件描述语言Verilog》等,强调了理论学习和实践操作的结合。

第二章专门研究Verilog应用,探讨了使用HDL设计的先进性,可能涉及具体的设计案例和优势分析,让学生更好地理解和掌握Verilog在实际项目中的作用。

通过本教程,学生将全面掌握Verilog语言的基础知识、设计流程、仿真技术以及关键工具的运用,为后续的数字集成电路设计打下坚实的基础。尽管缺失了第20章,但整体内容的完整性仍足以支持深入学习。

105 浏览量

2009-01-01 上传

2008-12-05 上传

2023-11-27 上传

2023-10-12 上传

2023-11-27 上传

2023-07-16 上传

2023-06-01 上传

2023-07-13 上传

zhdxaut

- 粉丝: 5

- 资源: 2

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析