FPGA在EDA/PLD中实现视频采集与显示的模块设计

115 浏览量

更新于2024-09-01

收藏 349KB PDF 举报

"EDA/PLD中的基于FPGA的视频采集与显示模块设计"

在电子设计自动化(EDA)和可编程逻辑器件(PLD)领域,基于FPGA的视频采集与显示模块设计是关键的技术之一。本文详细介绍了这样一个模块的设计过程,采用Altera公司的Cyclone II系列FPGA EP2c35F672c36作为核心处理单元,该器件拥有35000个逻辑单元,具备强大的数据处理能力。此外,模块配置了Epcs16作为主动串行配置器件,以实现FPGA的高效配置。

视频采集部分选用了分辨率为768×494像素的NTSC制式,配合输出像素为640×480的CCD摄像头,能够提供清晰的视频输入。在显示方面,设计中集成了VGA DAC(数模转换器)ADV7123,它包含了三个10位高速DAC,能确保高质量的图像输出。模块还支持VGA输出接口,可以连接到各种显示器设备。此外,模块还兼容NTSC和PAL两种常见的视频制式,通过视频解码器ADV7181进行解码,同时配备了RCA视频输入接口,方便接入不同的视频源。

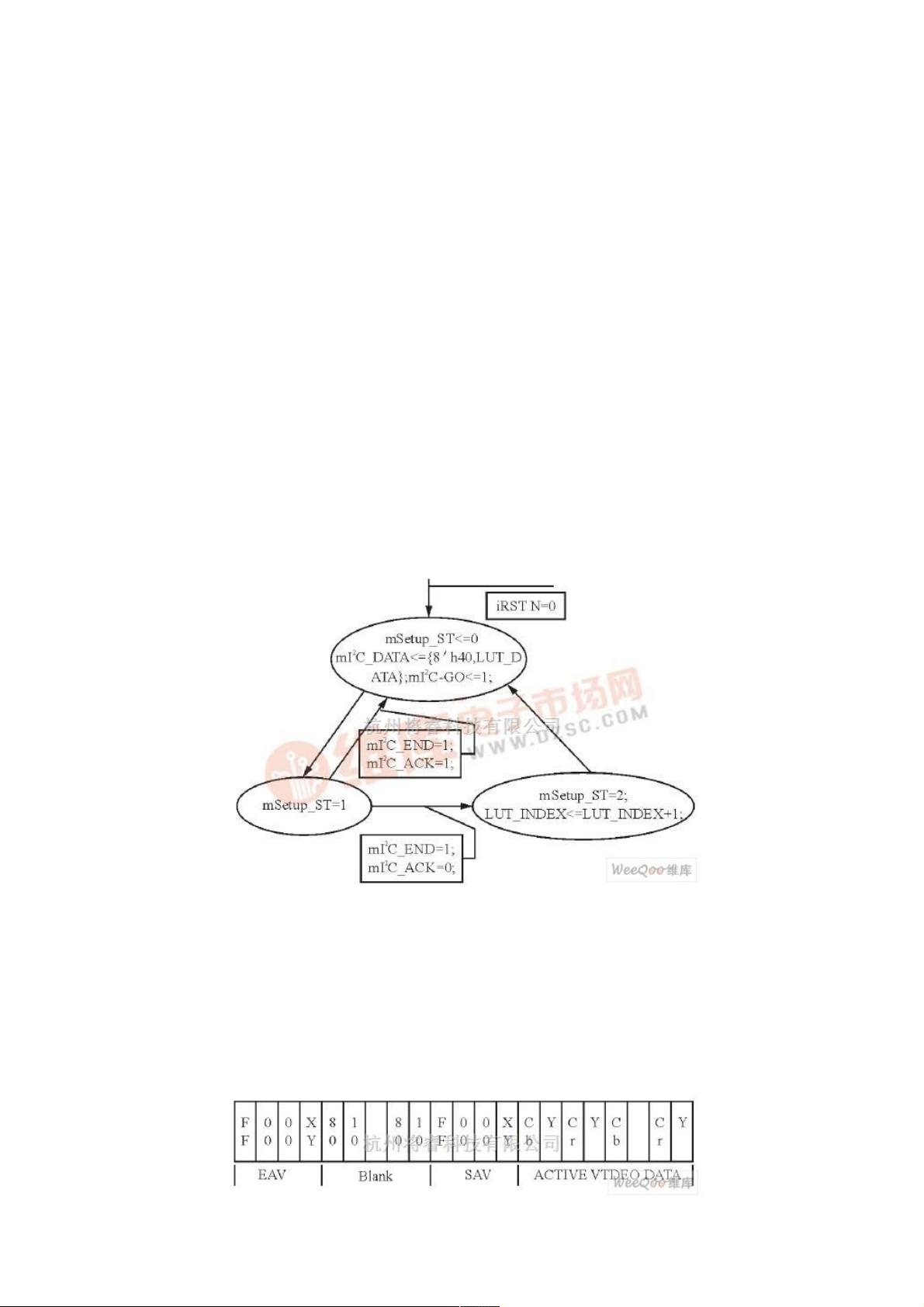

ADV7181是一款多功能的视频解码器,能够处理多种格式的模拟视频信号,如CVBS(复合视频基带信号)、S-VIDEO(分离视频)以及YPrPb分量视频。该解码器能够自动检测并适应NTSC、PAL和SECAM三种电视标准。其输出的YCrCb4:2:2视频数据与CCIR656标准兼容,包括垂直同步(VS)、水平同步(HS)和Blank等关键信号。为了充分利用ADV7181的功能,需要通过I2C总线对240个寄存器进行精确配置。在实际设计中,仅需要对其中40个寄存器进行参数设置,这就涉及到I2C_Controller和I2C_AV_config两个模块。

I2C_Controller模块负责I2C总线的数据传输控制,采用33个I2C时钟周期完成一次24位数据的传输,包括启动、数据传输和停止过程。SD_counter作为计数器,监控传输进度并控制数据的发送。而I2C_AV_config模块则专注于对ADV7181的寄存器进行配置,每个寄存器的设置通常需要经过三个步骤,确保视频信号的正确解码和显示。

这个基于FPGA的视频采集与显示模块设计综合运用了先进的FPGA技术、高效的配置方案以及高性能的视频解码器,实现了灵活、高质的视频处理功能,适用于多种应用场景,如监控、多媒体播放和工业控制等。这样的设计展示了EDA和PLD技术在现代电子系统设计中的重要作用,以及如何通过精心的硬件和软件协同设计,实现复杂视频处理系统的高效集成。

2020-11-29 上传

2020-11-07 上传

2020-11-07 上传

2020-11-09 上传

2020-10-20 上传

2020-11-04 上传

2020-11-29 上传

2020-11-08 上传

2020-11-11 上传

weixin_38567962

- 粉丝: 2

- 资源: 944

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载