多功能数字钟设计与实现 - 数字电路实验报告

版权申诉

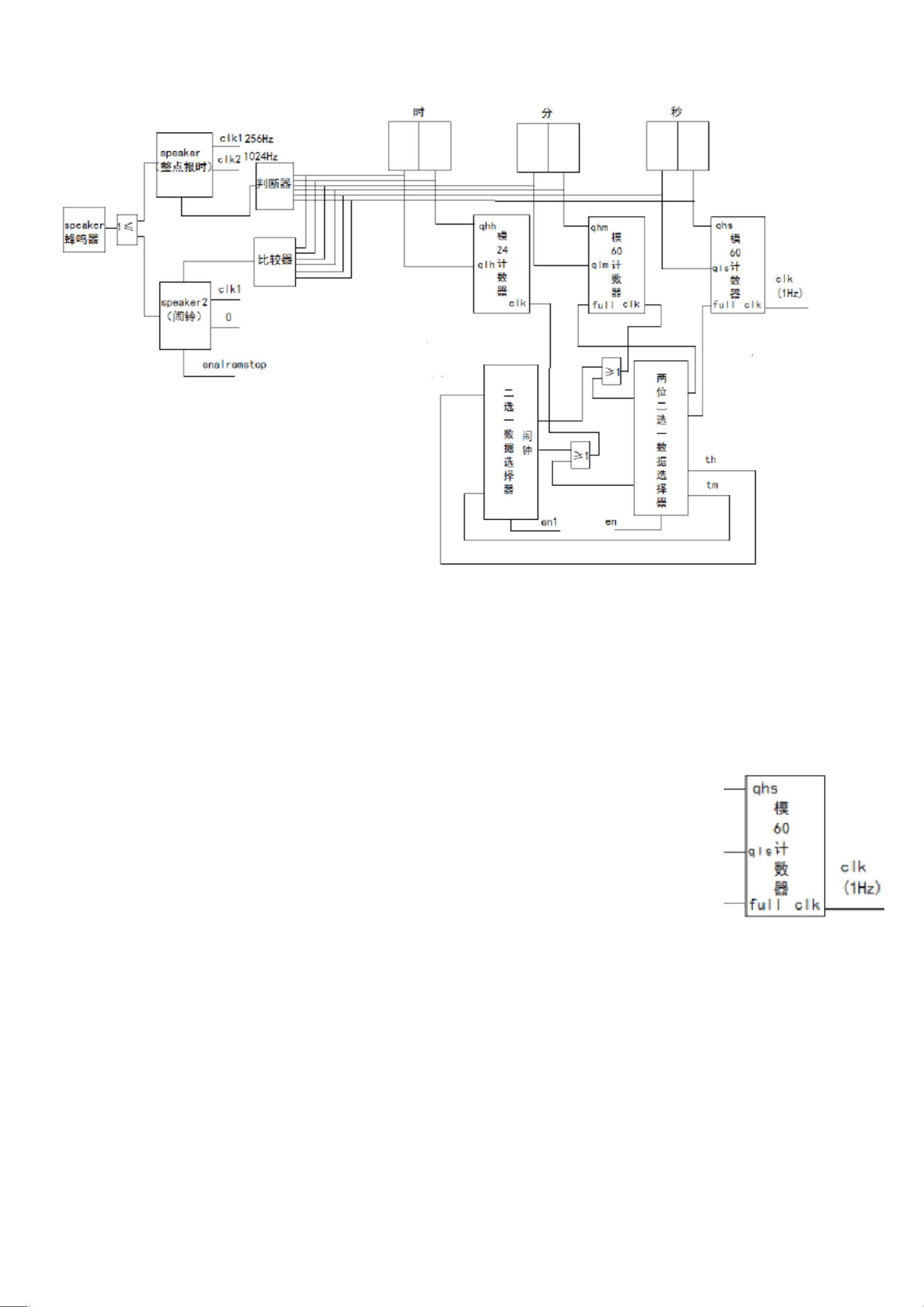

"这是一个关于数字电子技术实验的报告,主题是设计和实现一个多功能数字钟。实验涉及了数字电路基础知识,包括计数器设计、手动校时、定时与闹钟功能,以及整点报时功能。实验中使用了FPGA芯片,并通过VHDL语言进行编程。"

这篇报告详细介绍了大连理工大学本科学生在《数字电路课程设计》中的一个实验项目——多功能数字钟的设计和实现。该实验旨在训练学生对数字电路的理解和应用能力,特别是涉及到模数转换、计数器设计以及逻辑控制等方面的知识。

1. 设计要求:

- 实现一个显示小时、分钟和秒的十进制数字计时器,小时范围从00到23。

- 具备手动校时和校分的功能,允许用户调整时间。

- 包含定时与闹钟功能,能在预设时间触发闹铃。

- 整点报时,从59分54秒开始每隔2秒发出低音,连续3次,整点时则发出高音。

2. 设计分析与系统方案:

- 秒表部分通过模24和模60计数器实现24小时计时,确保准确无误。

- 在设置闹钟时,不应影响数字钟的正常运行,且应有独立的显示以供用户查看和设置。

- 调节闹钟时,应通过数码管清晰地展示当前设置。

3. 硬件电路设计:

- 实验中使用了FPGA最小系统,尽管课程未涵盖FPGA芯片的详细使用,但实验箱提供了必要的接口,如按键、LED、数码管等,需要学生设计相应的电路和参数。

- 开发系统采用GW48-CK的模式0,其中某些管脚如PIO7用于手动校时,PIO6、PIO5、PIO4分别用于调时、调分和闹钟设定等操作,其他管脚用于不同频率的时钟输入。

4. VHDL设计:

- VHDL语言用于描述系统的各个部分,包括系统结构和各个模块的功能。例如,模60计数器和模24计数器的实现是关键模块,它们需要通过VHDL的状态图或真值表来详细描述其工作原理。

- 系统原理图和主要模块的VHDL代码应完整展示,以体现设计的逻辑流程和功能实现。

这个实验报告涵盖了数字电路基础理论与实践的结合,让学生在实际操作中理解和掌握数字电路设计的基本技能。通过这样的项目,学生不仅能够学习到计数器设计、逻辑控制等基本概念,还能体验到硬件描述语言VHDL在实现复杂数字系统中的作用。

102 浏览量

2022-10-14 上传

828 浏览量

2022-07-13 上传

185 浏览量

2022-10-13 上传

春哥111

- 粉丝: 1w+

- 资源: 6万+

最新资源

- React性的

- Distributed-Blog-System:分布式博客系统实现

- CloseMe-crx插件

- 欧式建筑立面图纸

- 北理工自控(控制理论基础)实验报告

- yolov7升级版切图识别

- 作业-1 --- IT202:这是我的第一个网站

- hit-and-run:竞争性编程的便捷工具

- Pytorch-Vanilla-GAN:适用于MNIST,FashionMNIST和USPS数据集的Vanilla-GAN的Pytorch实现

- SNKit:iOS开发常用功能封装(Swift 5.0)

- 创意条形图-手机应用下载排行榜excel模板下载

- 项目36

- 通过混沌序列置乱水印.7z

- reactive-system-design

- getwdsdata.m:从 EPANET 输入文件中获取配水系统数据-matlab开发

- 100多套html模块+包含企业模板和后台模板(适合初级学习)