嵌入式Linux下的TFT液晶屏接口与信号时序分析

"液晶屏信号描述及时序分析"

液晶屏显示技术是电子设备中不可或缺的一部分,尤其是在嵌入式系统中。本文主要关注TFT液晶屏的信号描述和时序分析,这是理解和设计液晶屏驱动程序的基础。

TFT液晶屏的主要信号包括以下几个关键部分:

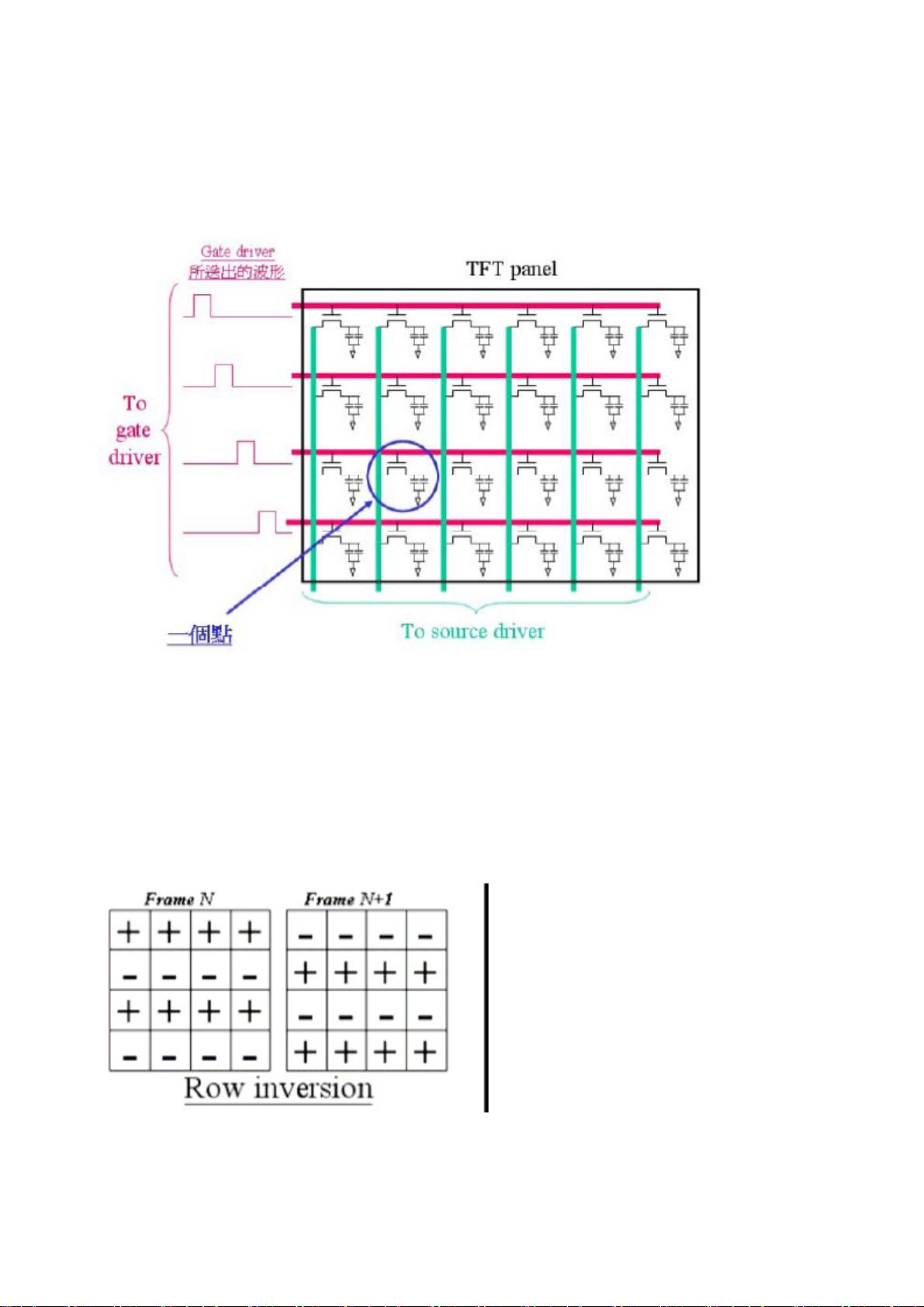

1. VSYNC(垂直同步信号):这个信号标志着一帧图像的开始,它在一个扫描周期内保持高电平,然后返回低电平,表示垂直扫描已完成并开始新的一帧。

2. HSYNC(水平同步信号):与VSYNC类似,HSYNC指示一行像素的开始和结束。在HSYNC高电平时,液晶屏开始读取一行数据;低电平时,表示行已读取完毕,进入下一行。

3. PCLK(像素时钟信号,也称为DCLK):提供像素数据传输的时钟脉冲,每一个PCLK的上升沿或下降沿对应一个像素的数据传输。

4. DE(Display Enable):显示使能信号,当DE为高时,液晶屏接收并处理来自控制器的数据。

5. BrightPWM(亮度脉宽调制)和Brightn(亮度控制):这些信号用于控制液晶屏的亮度。BrightPWM通常是一个脉宽调制信号,通过调整占空比来调节屏幕亮度;而Brightn则是一个使能信号,高电平开启背光,低电平关闭。

在基于嵌入式Linux的TFTLCDIP及驱动设计中,NiosII处理器扮演了核心角色。它在SDRAM中创建帧缓冲,用于存储待显示的图像数据。帧缓冲的大小通常根据屏幕分辨率和颜色深度来确定,例如640x480分辨率、16位RGB565格式的一帧图像需要640x480x2Bytes的空间。

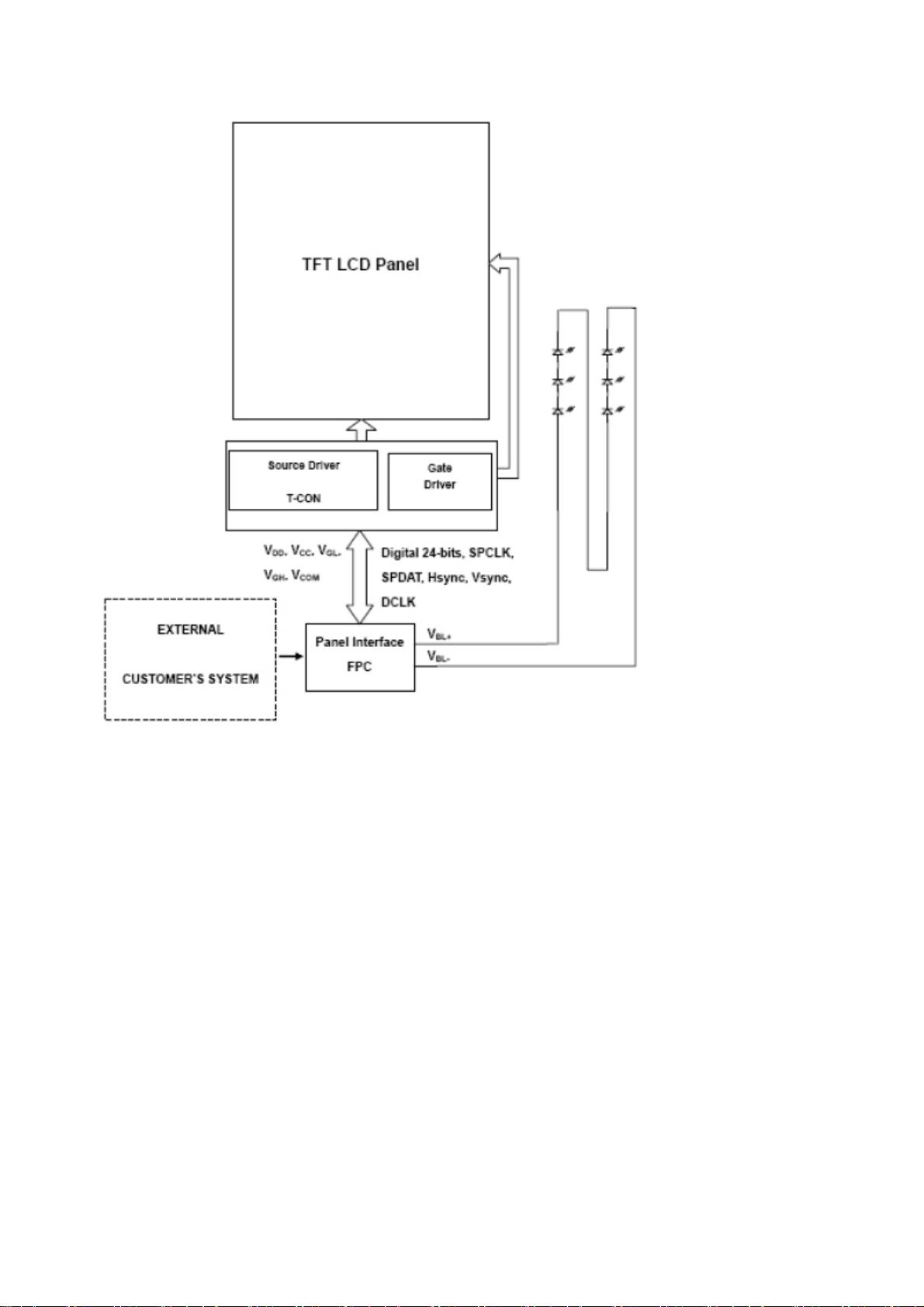

系统框图展示了AvalonBus如何连接各个模块,NiosII处理器通过AvalonBus与SDRAMController和LCDController通信。SDRAMController作为从设备,需要处理Processor和LCDController的请求,避免总线冲突。为此,AvalonBus引入了仲裁模块,动态分配总线使用权,保证系统的高效运行。

对于SDRAMController,数据传输带宽至关重要。以100MHz的SDRAM时钟频率为例,16位SDRAM的数据总带宽为200MByte/s。然而,一个640x480x2Bytes分辨率、60Hz刷新率的TFTLCD需要大约36MByte/s的带宽。这表明,除了LCD之外,处理器还需要处理其他任务,对总线资源的管理成为优化系统性能的关键。

LCD控制器通常通过FPGA实现,包含Avalon从总线接口模块和DMAMaster接口模块。从总线接口负责与处理器交互,控制LCD显示参数,而DMAMaster则负责按需从内存中读取数据并传输给LCD。这些寄存器允许用户设定LCD控制器的工作模式和获取其工作状态,确保屏幕正确显示。

液晶屏的信号描述和时序分析是理解显示系统工作原理的关键,而在嵌入式系统中,有效的总线管理和硬件资源优化对于实现高效、流畅的显示至关重要。

2020-08-10 上传

2018-12-25 上传

2012-12-27 上传

2021-10-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

jangyouhua

- 粉丝: 0

- 资源: 4

最新资源

- Java毕业设计项目:校园二手交易网站开发指南

- Blaseball Plus插件开发与构建教程

- Deno Express:模仿Node.js Express的Deno Web服务器解决方案

- coc-snippets: 强化coc.nvim代码片段体验

- Java面向对象编程语言特性解析与学生信息管理系统开发

- 掌握Java实现硬盘链接技术:LinkDisks深度解析

- 基于Springboot和Vue的Java网盘系统开发

- jMonkeyEngine3 SDK:Netbeans集成的3D应用开发利器

- Python家庭作业指南与实践技巧

- Java企业级Web项目实践指南

- Eureka注册中心与Go客户端使用指南

- TsinghuaNet客户端:跨平台校园网联网解决方案

- 掌握lazycsv:C++中高效解析CSV文件的单头库

- FSDAF遥感影像时空融合python实现教程

- Envato Markets分析工具扩展:监控销售与评论

- Kotlin实现NumPy绑定:提升数组数据处理性能