晶振负载电容计算与匹配电容选择详解

需积分: 13 162 浏览量

更新于2024-08-05

收藏 308KB DOCX 举报

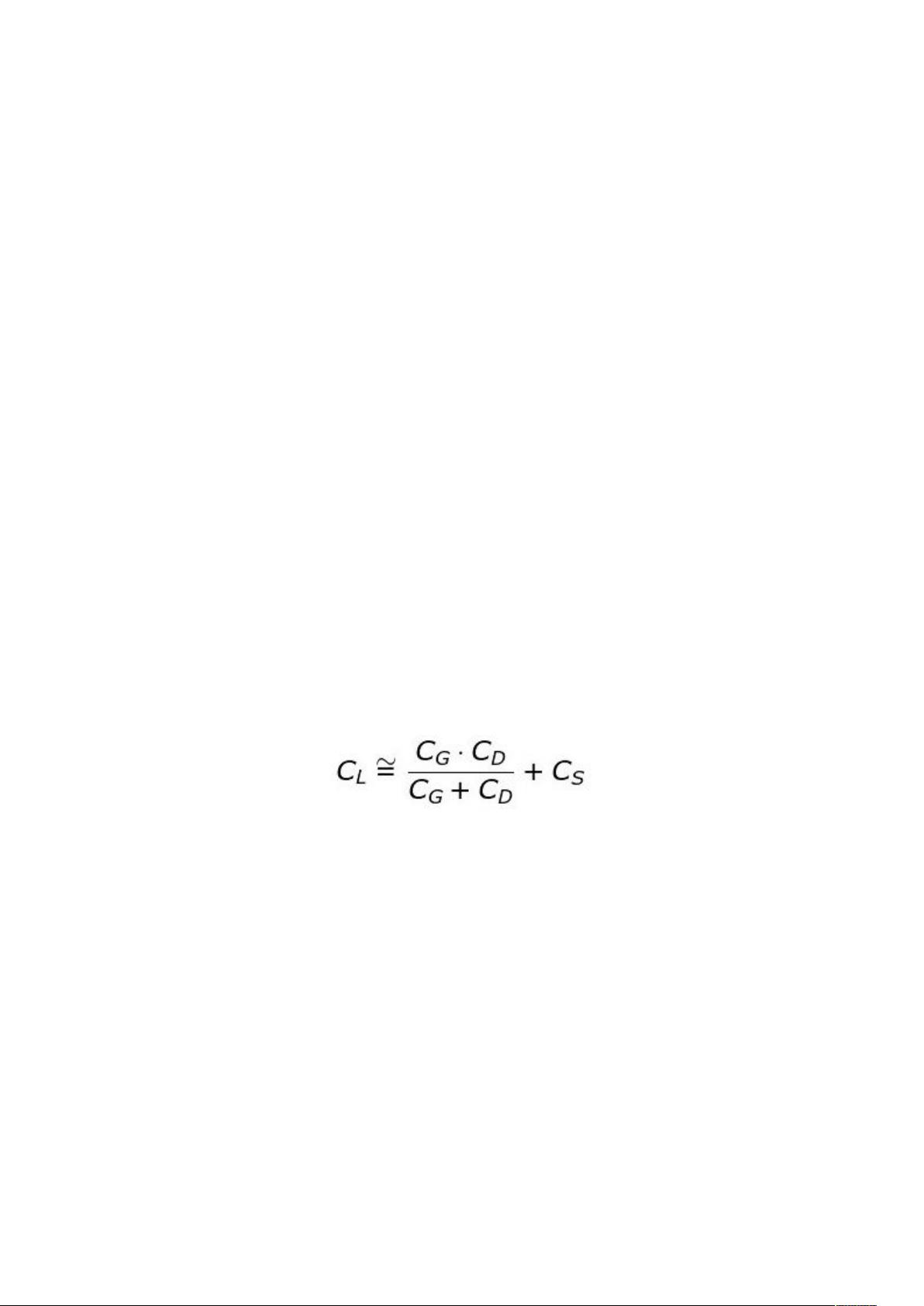

本文档深入探讨了在晶振振荡电路设计中,如何结合晶振的负载电容来计算外匹配电容的容值,并关注在设计过程中的注意事项。首先,理解晶振负载电容至关重要,它是指晶体元件两端的总有效电容,包括晶体自身的静噪电容(CS,通常由制造商提供,范围在0.2pF至8pF之间)、电路板到地的寄生电容(CG和CD,包括主芯片管脚寄生电容Ci、PCB走线寄生电容CPCB和外加匹配电容CL1/CL2)以及可能的IC输入端对地电容。负载电容直接影响振荡频率,通常通过调整电容来确保工作频率接近标称值。

在选择外匹配电容(CL1和CL2)时,设计者需要考虑晶振的实际负载电容与其标称值的匹配,因为负载电容与频率之间的关系非线性:当负载电容减小时,频率偏差增大;反之,增大负载电容,频率偏差减小。例如,图3展示了当使用22pF负载电容时,晶振频率误差与负载电容的关系。

计算外匹配电容的具体方法是,如果实际等效电容与标称负载电容不符,设计者需要通过调整CL1和CL2来补偿这种差异,以确保晶振稳定工作在预期的频率。这个过程可能涉及到对电路板布局、电容选择和电路补偿技术的精确控制,以最小化振荡频率的偏离。

在设计过程中,需要注意的事项包括但不限于:

1. 选择合适的负载电容标准值(如12.5pF、16pF、20pF、30pF等),并在必要时进行微调。

2. 优化电路板设计以减少寄生电容的影响,比如使用低阻抗走线、合理布局晶体和匹配电容。

3. 考虑晶体的温度漂移和老化效应,这些因素也可能影响负载电容和频率稳定性。

4. 对于高精度应用,可能需要进行温度补偿或使用温度补偿型晶振。

5. 在电路调试阶段,使用频率计测量实际工作频率,并根据测量结果调整匹配电容。

晶振匹配电容的设计是一个关键环节,它要求设计师具备深厚的模电理论基础,熟练运用计算和分析技巧,以确保晶振振荡电路的性能稳定和精度。

178 浏览量

2021-09-27 上传

2021-10-02 上传

2021-11-17 上传

2022-06-19 上传

2024-07-05 上传

2021-09-27 上传

2022-07-08 上传

2022-11-28 上传

Bob_bate

- 粉丝: 28

- 资源: 9

最新资源

- 2013年 " 蓝桥杯 "第五届全国软件和信息技术专业人才大赛 嵌入式设计与开发项目模拟试题——·双路输出控制器·代码.zip

- CookingApp_v1

- 国际象棋

- 图形窗口生成器 fig.m,版本 3.1:打开具有指定大小的新图形窗口-matlab开发

- front-end-samples:前端样本

- 电路方面的仿真操作 资料

- AR256_Demon_killers:预测棉花的未来价格趋势并提出合适的价格模型并缩小买卖双方之间的差距(SIH-2020)

- My-OOP-endterm-project:Bakhytzhan SE-2016

- rest:基于 https 的流星休息

- EI会议海报可编辑模板,高效解决新手小白对不知道如何制作海报的困惑

- 保险行业培训资料:一诺千金产品基础班

- state-csv.zip

- 图书馆应用

- 带有 3D 误差条的简单条形图:带有 3D 误差条的简单条形图。-matlab开发

- 保险公司讲师邀请函版本

- tamplated-road-trip