"时序逻辑电路触发器及设计分析:基本 RS、同步、主从、边沿触发器转换方法"

版权申诉

173 浏览量

更新于2024-04-03

收藏 1.54MB PPT 举报

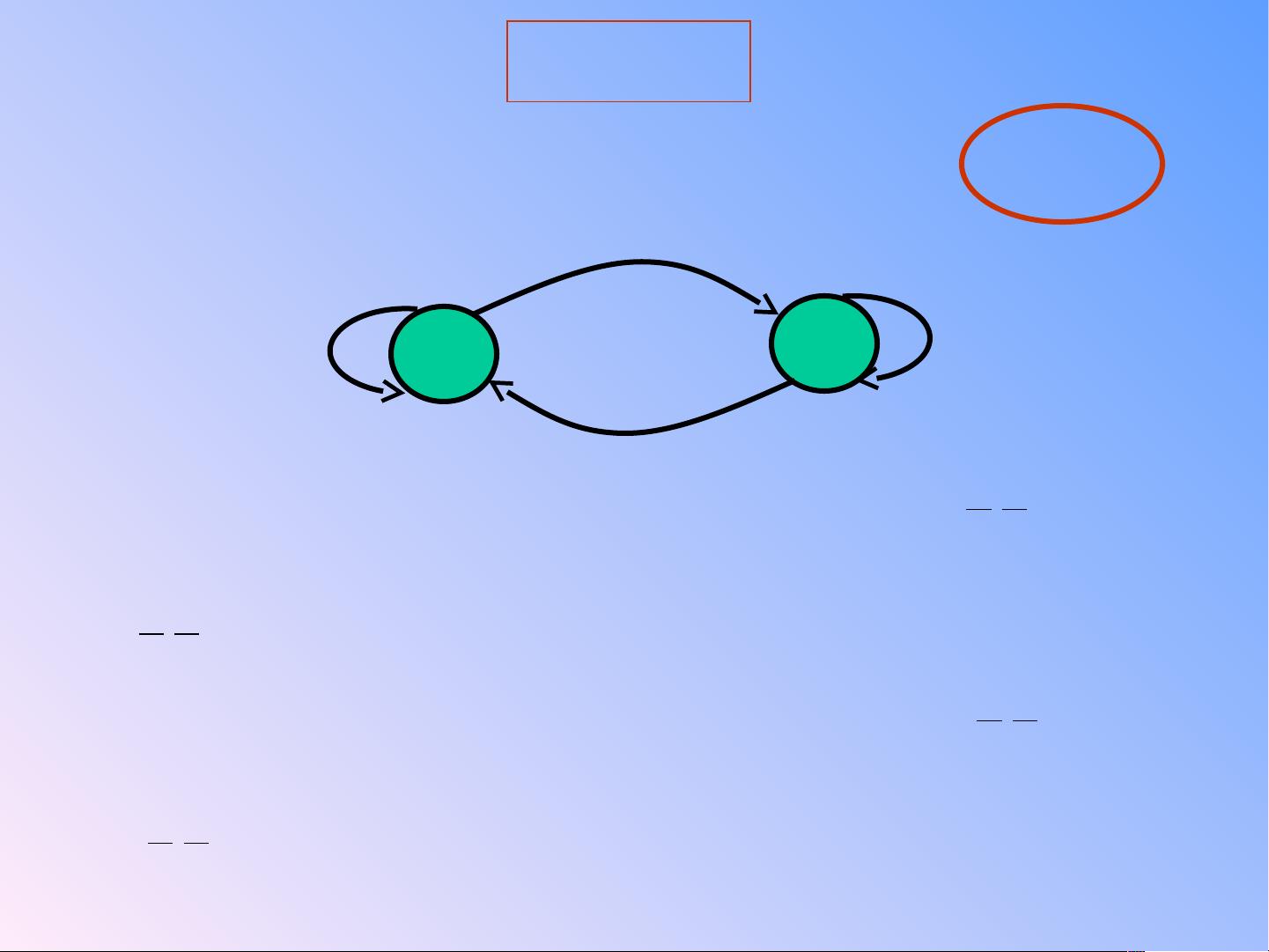

数字电路课件中的第四章介绍了时序逻辑电路,主要涵盖了触发器的概念、分析和设计。触发器作为构成时序逻辑电路的基本逻辑部件,具有两个稳定的状态:0状态和1状态。在不同的输入情况下,触发器可以切换到0状态或1状态,并且可以在输入信号消失后保持其状态不变,从而能够记忆1位二值信号。根据逻辑功能的不同,触发器可以分为RS触发器、D触发器、JK触发器、T和T´触发器;按照结构形式的不同,又可分为基本RS触发器、同步触发器、主从触发器和边沿触发器。

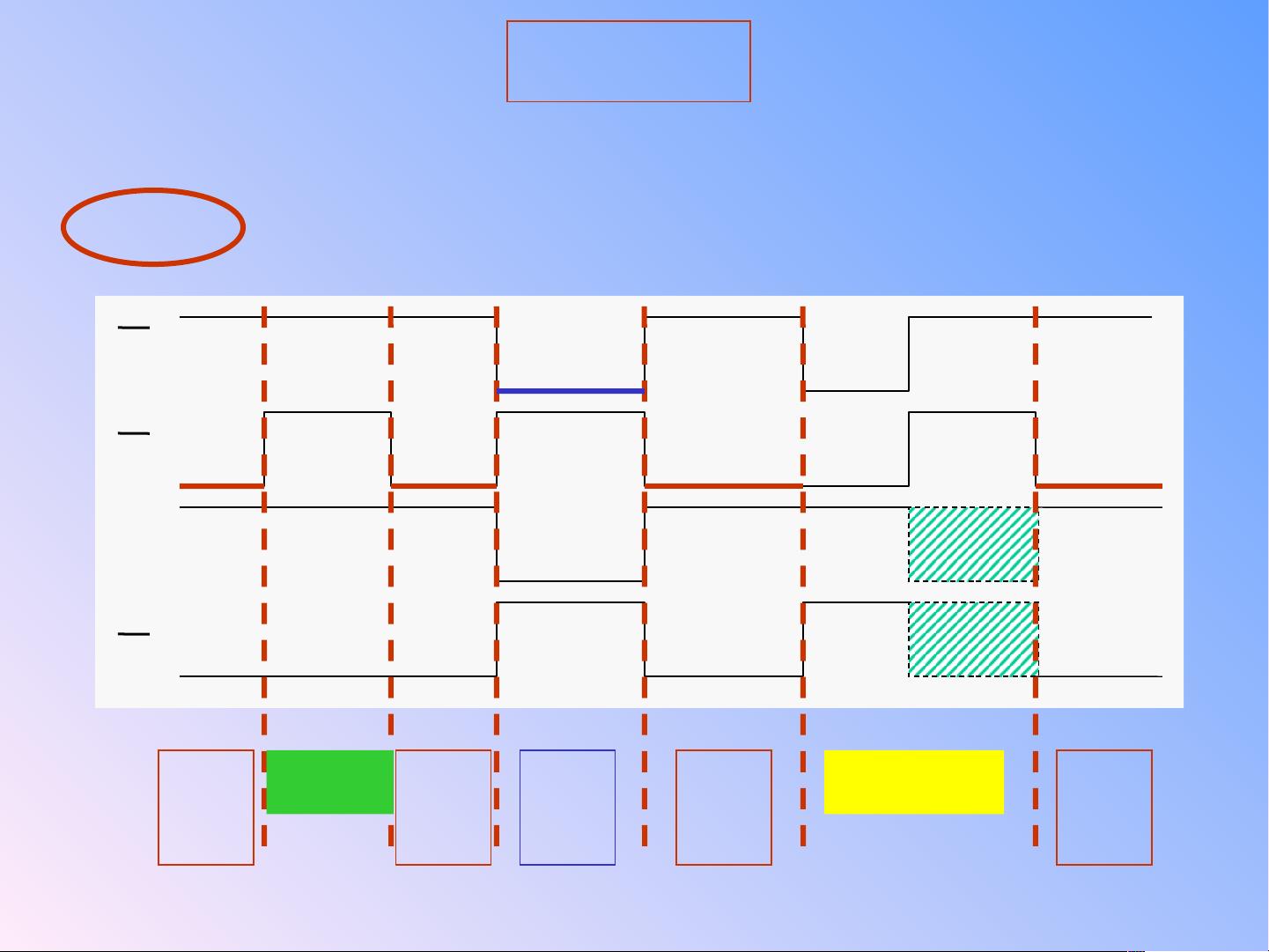

基本RS触发器的电路组成和逻辑符号如下:信号输入端为SR,并且低电平有效。信号输出端有两个状态,分别为Q=0、Q=1和Q=1、Q=0。当输入为低电平时,Q输出为高电平,反之亦然。基本RS触发器是一种最简单的触发器,通过控制输入信号的方式来实现状态的改变。在设计时序逻辑电路时,可以根据具体的需求选择不同类型的触发器,以实现特定的功能和逻辑运算。在时序逻辑电路中,触发器的重要性不言而喻,它们承担着存储信息、实现状态转换等重要任务。

除了基本RS触发器外,课件还介绍了同步触发器、主从触发器和边沿触发器等不同类型的触发器。同步触发器通过时钟信号来控制状态的改变,主从触发器通过主触发器和从触发器的组合来实现更复杂的逻辑运算,而边沿触发器则是在触发器输入信号的上升或下降沿进行状态的切换。不同类型的触发器之间可以相互转换和组合,以满足不同的逻辑设计需求。

在时序逻辑电路的设计中,触发器扮演着重要的角色。它们的稳定状态、状态转换和记忆功能为时序逻辑电路的正常运行提供了基础支持。通过学习触发器的原理和设计方法,我们可以更好地理解时序逻辑电路的工作原理,从而设计出更加高效和稳定的数字电路系统。触发器的应用领域广泛,涵盖了数字电子、通信系统、计算机等多个领域,对于提高系统的性能和稳定性具有重要意义。

总之,时序逻辑电路中的触发器是一种重要的逻辑部件,具有记忆、控制和状态转换等功能。通过学习和掌握触发器的原理和设计方法,我们可以更好地理解和应用时序逻辑电路,为数字电路领域的发展和应用提供有力支持。触发器的不断改进和创新将进一步推动数字电路技术的发展,为人类社会的科技进步做出更大的贡献。

相关推荐

wxg520cxl

- 粉丝: 26

最新资源

- Web程序页面菜单导航的实现与应用

- C#实现带音乐播放功能的迷宫游戏教程

- JavaScript测试调试技术:初学者的全面指南

- 凹丫丫中小型网站客户管理系统功能介绍

- VC开发的印刷体汉字识别系统

- Matlab实现GIRF计算与应用教程

- 探索易语言实现BUX网络验证的奥秘

- Java编程教学:贪吃蛇游戏的源码解析

- 全面详尽的数据挖掘与数据仓库宝典

- HEVC/H.265最新版本HM-12.0参考代码发布

- Visual C++ 2005编程入门:源码与习题解答

- Instant_Test:多选模拟考试系统应用与开发

- Lodop控件使用教程:打印样式、条码、二维码及优化输出

- 易语言实现简易BP神经网络教程与源码

- NOKIA 1681c 和 1680c 驱动安装方法及软件

- BatTool 1.3.5:批处理文件图形化与批量处理工具