VHDL实现的彩灯控制器与16进制减法计数器设计

需积分: 12 60 浏览量

更新于2024-07-31

收藏 302KB DOCX 举报

"该资源主要涉及使用VHDL语言设计电子工程中的彩灯控制器和计数器,通过自顶向下的设计方法实现16进制减法计数器的动态显示,包括四位二选一扫描电路、共阴极7段译码器、16进制减法计数器、二进制分位、分频器等关键模块。"

在电子设计自动化(EDA)领域,VHDL是一种重要的硬件描述语言,用于设计和仿真数字逻辑系统。在这个项目中,VHDL被用来构建一个功能丰富的系统,其中包括以下几个核心部分:

1. **KZ模块**:这是一个二选一扫描电路,其作用是根据时钟信号CLK切换高位或低位输出,并通过位选信号D来决定LED管显示的数据。Q(3:0)是数据输出端口,D(2:0)则是位选通信号。

2. **see_led7模块**:这是一个共阴极7段译码器,将输入的二进制信号转换为0-9的数字显示在7段LED上,适用于共阴极类型的LED显示器。

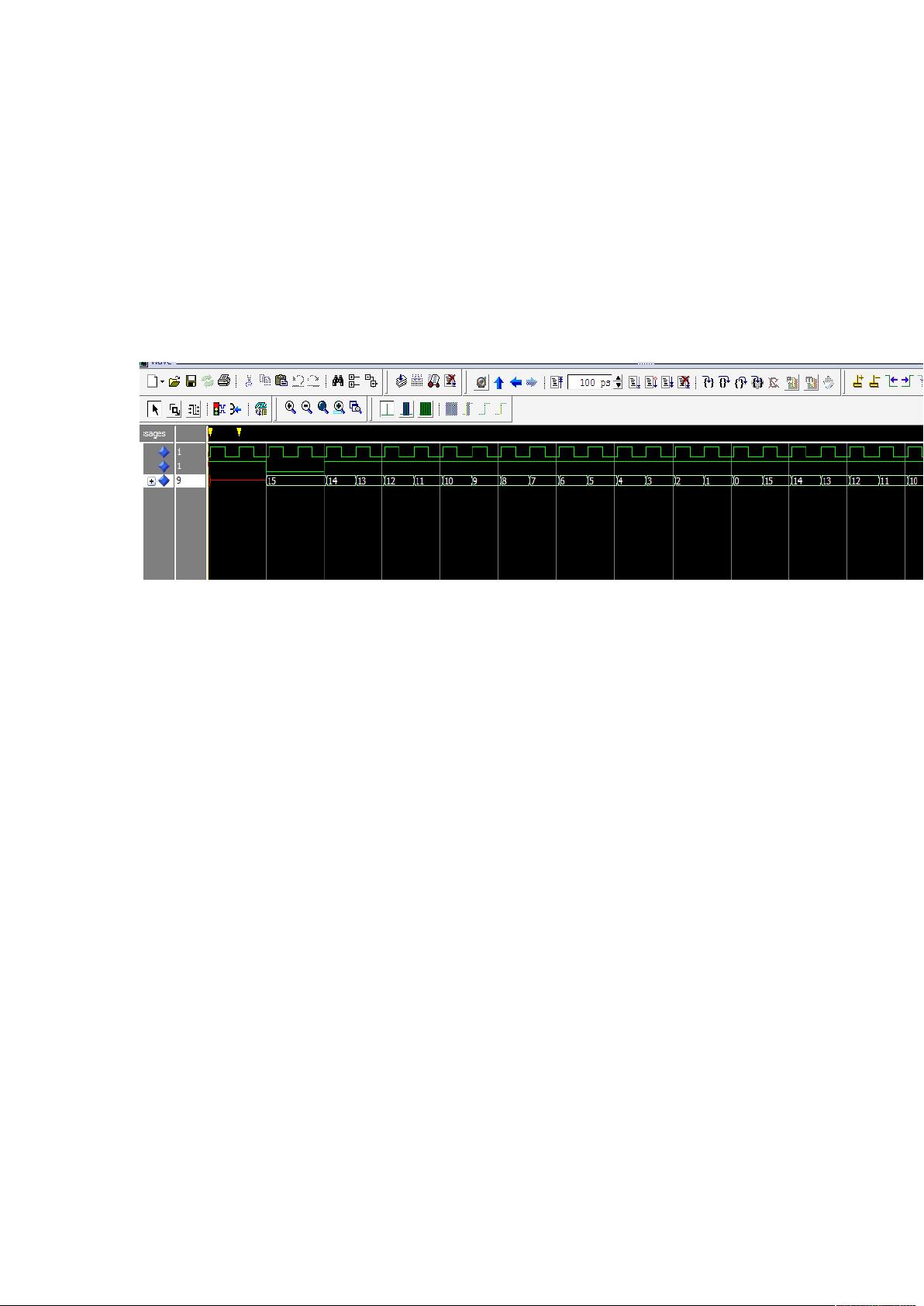

3. **jsq16模块**:这是16进制减法计数器,基于时钟信号CLK进行减法计数,从15递减至0,形成一个循环,并提供一个复位按钮功能。

4. **gdf模块**:将16进制数分成高位和低位,以便进行独立处理,这对于显示和计算两位的16进制数至关重要。

5. **fp107和fp5e4模块**:这两个是分频器,分别将10MHz的时钟信号分频为1Hz和200Hz,以满足不同频率需求的计数器或控制电路。

实验内容包括了VHDL代码的编写,以及对每个模块进行仿真验证,确保它们能正确执行预期功能。KZ模块的VHDL代码展示了如何使用输入信号如CLK、EN、H和L来控制输出Q和D。这种设计方法强调了模块化,使得设计更易于理解和调试,同时也方便在实际硬件上实现。

这个项目提供了实践VHDL语言的机会,涵盖了数字逻辑设计的基础概念,如扫描电路、译码器、计数器、分频器等,这些都是现代数字系统设计的关键组件。通过这种方式,学习者可以深入理解数字系统的工作原理,并具备将软件描述转化为实际硬件的能力。

149 浏览量

2692 浏览量

237 浏览量

2024-11-13 上传

141 浏览量

2021-10-04 上传

315 浏览量

171 浏览量

113 浏览量

普通网友

- 粉丝: 0

- 资源: 3

最新资源

- QuantitativeRiskSim:定量风险模拟工具

- 【机器学习实战】第十章 K-Means算法数据集-数据集

- oxefmsynth:Oxe FM Synth 官方仓库

- emailwhois:使用Python在所有已知域中查找电子邮件域(@ example.com)

- rary:lib + rary + .so

- QYBot:契约机器人框架

- 3D打印的恶作剧振动杯-项目开发

- UQCMS云商-B2B2C系统 v1.1.17101822

- jekyll-liquid-plus:用于更智能 Jekyll 模板的超强液体标签

- 使用springmvc框架编写helloworld,使用eclispe开发工具

- apollo-mobx:使用React高阶组件的Apollo MobX映射...以及更多

- Fivek.github.io

- DrawTree.rar

- 用verilog语言编写的交通灯控制器实现.rar

- 和弦音乐-复仇者联盟-项目开发

- dbcopier:将数据从一个 MySQL 数据库表复制到另一个