基于Multisim的74LS74N多路抢答器设计与原理分析

"这篇资源是关于使用Multisim设计多路抢答器的教程,涵盖了控制电路、封锁电路和编码电路的设计,涉及了74LS74N和74LS00N、74LS08N、74LS147N等集成电路的运用。"

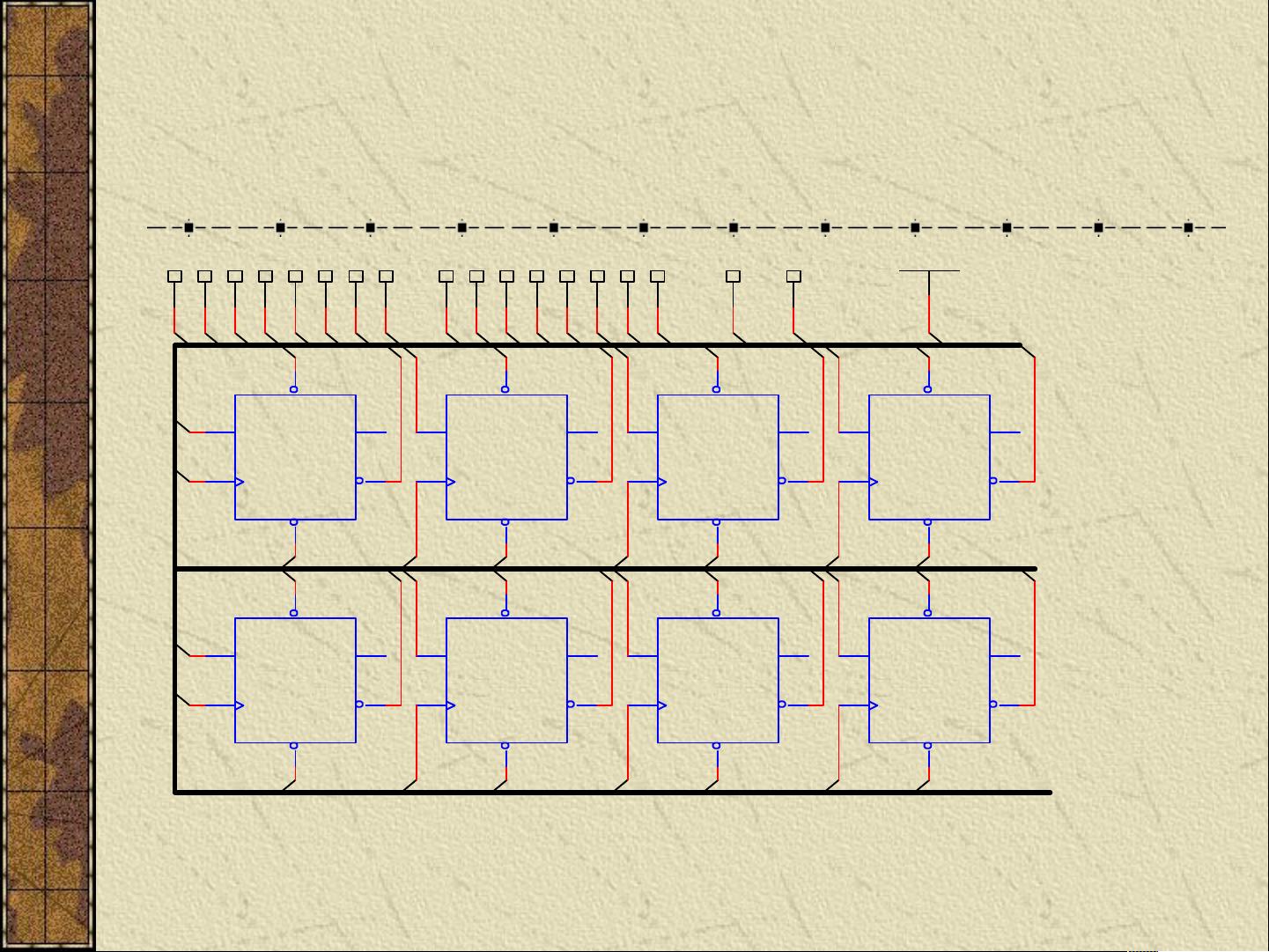

在电子工程领域,多路抢答器是一种常见的竞赛设备,用于确保参赛者在正确的时间进行抢答。本设计使用了Multisim这一模拟软件进行仿真,下面是详细的步骤和原理:

1. **控制电路设计**:

控制电路的核心是74LS74N双D触发器(如U1A到U4B),它们用于存储和传递抢答状态。每个触发器都有D输入、输出Q和非Q、清除(CLR)和时钟(CLK)端口。当CLR为低电平时,触发器处于复位状态,所有输出均为低电平;当CLK脉冲到来时,如果D输入为高,则输出Q将被置为高,表示抢答成功。这种设计可以确保只有在特定时刻,即主持人开启抢答后,参赛者的抢答信号才会被记录。

2. **封锁电路**:

抢答器的封锁电路(如U1A至U3C中的74LS00N和74LS08N)用于防止多个参赛者同时抢答。74LS00N是四2输入与非门,74LS08N是四2输入与门,它们组合起来可以实现逻辑判断,确保在任何时候只有一个输入可以被识别为有效。一旦有选手成功抢答,封锁电路会阻止其他选手的信号通过,直到当前抢答状态解除。

3. **编码电路**:

编码电路(如U5中的74LS147N)的作用是将各个参赛者的抢答信号转换为唯一的数字输出。74LS147N是8线-3线优先编码器,当某一路输入(IO1至IO8)为高电平时,对应的输出(A、B、C)将根据其位置给出一个二进制编码。例如,如果IO1被激活,输出A为1,B和C为0,这样就可以明确识别出是哪位选手成功抢答。

4. **整体工作流程**:

在抢答过程中,主持人首先启动控制电路,清除所有触发器的输出,然后通过时钟信号允许抢答。选手们在看到提示后按下各自的按钮,触发器接收到输入并根据时钟脉冲更新状态。封锁电路保证只有一个选手的信号能够通过,而编码电路则将该选手的编号编码成数字输出,显示在计分板上。

这个设计不仅提供了基本的抢答功能,还考虑到了公平性和准确性,使得比赛更加公正有序。通过Multisim这样的模拟工具,可以方便地进行电路的布局、仿真和测试,确保设计的可靠性和有效性。此外,了解74系列集成电路的使用对于电子爱好者和工程师来说是非常基础且重要的技能,因为这些芯片在很多实际应用中都有广泛的应用。

543 浏览量

455 浏览量

113 浏览量

110 浏览量

321 浏览量

997 浏览量

2010-01-11 上传

151 浏览量

susan9595

- 粉丝: 0

最新资源

- Linux平台PSO服务器管理工具集:简化安装与维护

- Swift仿百度加载动画组件BaiduLoading

- 传智播客C#十三季完整教程下载揭秘

- 深入解析Inter汇编架构及其基本原理

- PHP实现QQ群聊天发言数统计工具 v1.0

- 实用AVR驱动集:IIC、红外与无线模块

- 基于ASP.NET C#的学生学籍管理系统设计与开发

- BEdita Manager:官方BEdita4 API网络后台管理应用入门指南

- 一天掌握MySQL学习笔记及实操练习

- Sybase数据库安装全程图解教程

- Service与Activity通信机制及MyBinder类实现

- Vue级联选择器数据源:全国省市区json文件

- Swift实现自定义Reveal动画播放器效果

- 仿53KF在线客服系统源码发布-多用户版及SQL版

- 利用Android手机实现远程监视系统

- Vue集成UEditor实现双向数据绑定