基于Cyclone系列FPGA的SEP3203数据通信接口设计

136 浏览量

更新于2024-08-31

收藏 355KB PDF 举报

SEP3203处理器的FPGA数据通信接口设计

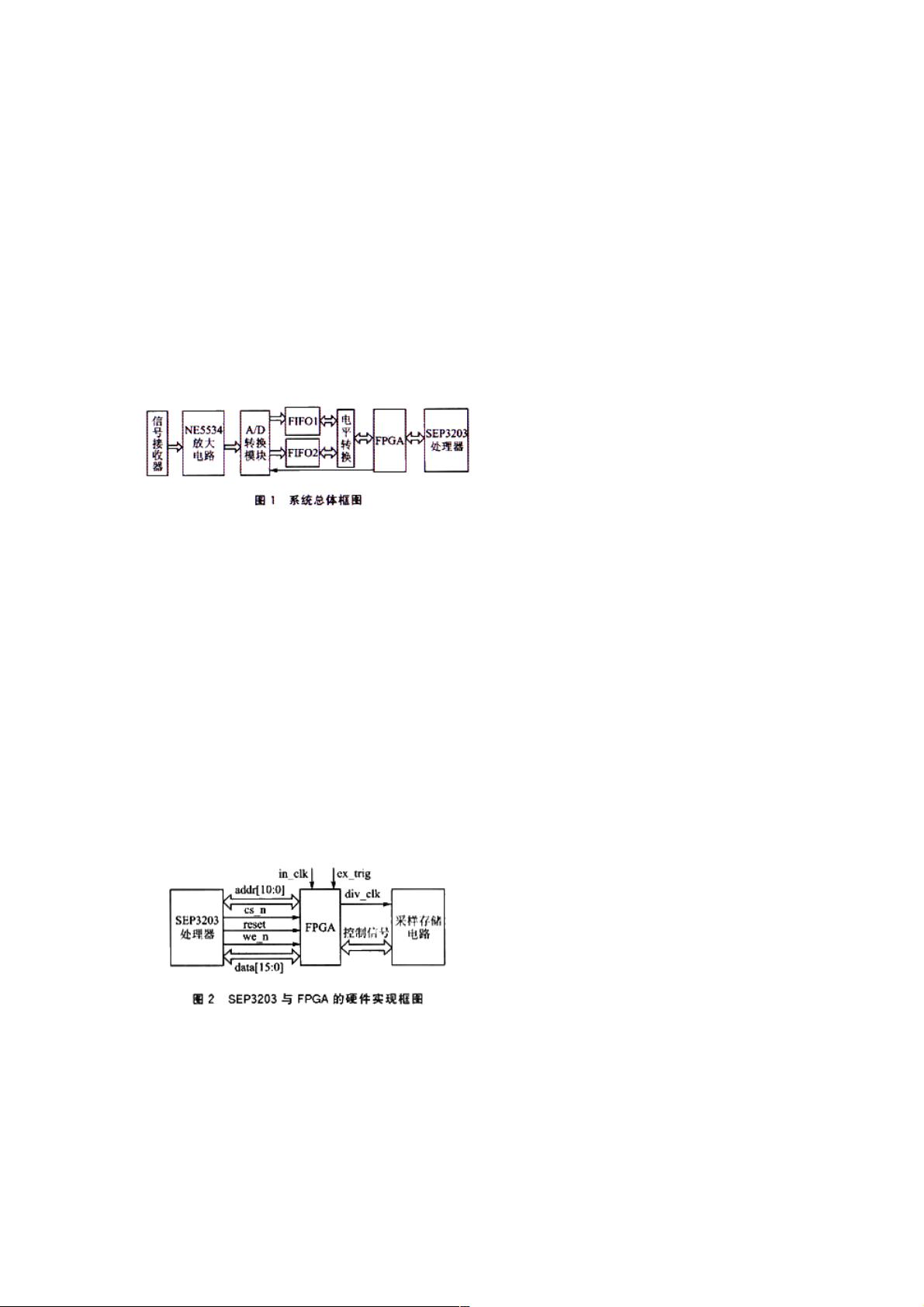

本文主要讲述了SEP3203处理器的FPGA数据通信接口设计,系统中使用的FPGA为Altera公司的Cyclone系列中的EP1C6Q240C8,拥有丰富的I/O资源和逻辑资源,外部接口遵循SRAM时序。本设计主要负责提供信号的A/D采样频率,并将A/D转换后的数据存储到一组FIFO中,待FIFO的FF(Full Flag)端口有效后,将FIFO中的数据读回,同时使能另一组FIFO的写时序,实现了信号不间断的采样和存储。

知识点一:FPGA在数据通信接口设计中的应用

FPGA(Field-Programmable Gate Array)是一种基于可编程逻辑器件的集成电路,具有高度的灵活性和可编程性。FPGA可以根据不同的应用场景进行编程和配置,以满足不同的需求。在本设计中,FPGA主要负责提供信号的A/D采样频率,并将A/D转换后的数据存储到一组FIFO中。

知识点二:A/D转换技术在数据采样中的应用

A/D转换(Analog-to-Digital Converter)是一种将模拟信号转换为数字信号的技术。A/D转换器可以将模拟信号转换为数字信号,以便于数字信号处理和存储。在本设计中,A/D转换芯片使用了ADI公司的AD1672,它采用4级流水线结构,在3Msps采样速度下精度为12位。

知识点三:FIFO在数据存储中的应用

FIFO(First-In-First-Out)是一种数据存储器件,能够存储和处理大量的数据。在本设计中,FIFO选用了IDT公司的IDT7202,它具有输入和输出两套数据线,独立的读/写地址指针在读/写脉冲的控制下顺序地从双口FIFO读/写数据。

知识点四:FPGA与SEP3203处理器之间的数据通信

SEP3203处理器是一种高性能的处理器,能够处理大量的数据。在本设计中,FPGA将一组数据处理完毕后,以中断的方式通知SEP3203,处理器以DMA方式将运算后的结果存储到片外的SDRAM中。由于数据写满FIFO的时间大于FPGA处理数据的时间,所以整个系统实现了流水线操作。

知识点五:电平转换技术在数据通信中的应用

电平转换是一种将不同电平的信号转换为相同电平的技术。在本设计中,FPGA将数据从FIFO读入内部存储器时,需要经过一个电平转换芯片。系统选用了IDT公司的IDT74LVC16245,它支持8/16位数据的双向传输。

本设计展示了FPGA在数据通信接口设计中的应用,包括A/D转换技术、FIFO在数据存储中的应用、FPGA与SEP3203处理器之间的数据通信和电平转换技术等多个知识点。

weixin_38746818

- 粉丝: 7

- 资源: 910

最新资源

- 社交媒体营销激励优化策略研究

- 终端信息查看工具:qt框架下的输出强制抓取

- MinGW Win32 C/C++ 开发环境压缩包快速入门指南

- STC8G1K08 PWM模块实现10K频率及易改占空比波形输出

- MSP432电机驱动编码器测路程方法解析

- 实现动静分离案例的css/js/img文件指南

- 爱心代码五种:高效编程的精选技巧

- MATLAB实现广义互相关时延估计GCC的多种加权方法

- Hive CDH Jar包下载:免费获取Hive JDBC驱动

- STC8G单片机实现EEPROM及MODBUS-RTU协议

- Java集合框架面试题精讲

- Unity游戏设计与开发资源全集

- 探索音乐盒.zip背后的神秘世界

- Matlab自相干算法GUI界面设计及仿真

- STM32智能小车PID算法实现资料

- Python爬虫实战:高效爬取百度贴吧信息