"数字系统设计与Verilog HDL(第7版)PPT资源详解"

需积分: 0 152 浏览量

更新于2024-01-08

2

收藏 42.22MB PDF 举报

【考研复习资源】数字系统设计与Verilog HDL (第7版)PPT是一份详细的教程,由知名专家John F. Wakerly教授编写。这个资源涵盖了数字系统设计和Verilog HDL的核心知识,适用于准备参加研究生考试的电子、计算机、自动化等专业的学生,同时也适用于正在学习数字系统设计和Verilog HDL的本科生和相关领域的工程师和技术人员。

这个PPT资源共分为五个章节,内容包括了数字系统和计算机概述、逻辑代数基础、基本逻辑门、组合逻辑电路和触发器。第一章介绍了数字系统和计算机的基本概念和发展历程,给读者提供了对数字系统设计的初步了解。第二章介绍了逻辑代数的基本概念和运算规则,包括布尔代数和三态逻辑等。第三章介绍了基本的逻辑门,包括与门、或门、非门、与非门、或非门等。第四章介绍了组合逻辑电路的设计和分析方法,包括编码器、译码器、多路选择器、比较器等。第五章介绍了触发器,包括RS触发器、D触发器、JK触发器等。

此外,该PPT资源还涉及了Verilog HDL的基础知识和应用。Verilog HDL是一种硬件描述语言,常用于数字系统设计。它能够描述电路结构和行为,方便设计人员进行数字系统的设计和验证。通过学习Verilog HDL,读者可以了解到如何使用这门语言来描述和实现数字系统。

这个PPT资源的学习目的主要有三个:理解一类器件、掌握一门语言、熟悉几种EDA软件。学习者将能够理解数字系统中常见的器件和其工作原理,掌握Verilog HDL这门语言的语法和使用方法,同时还能够熟悉几种EDA软件工具的使用。

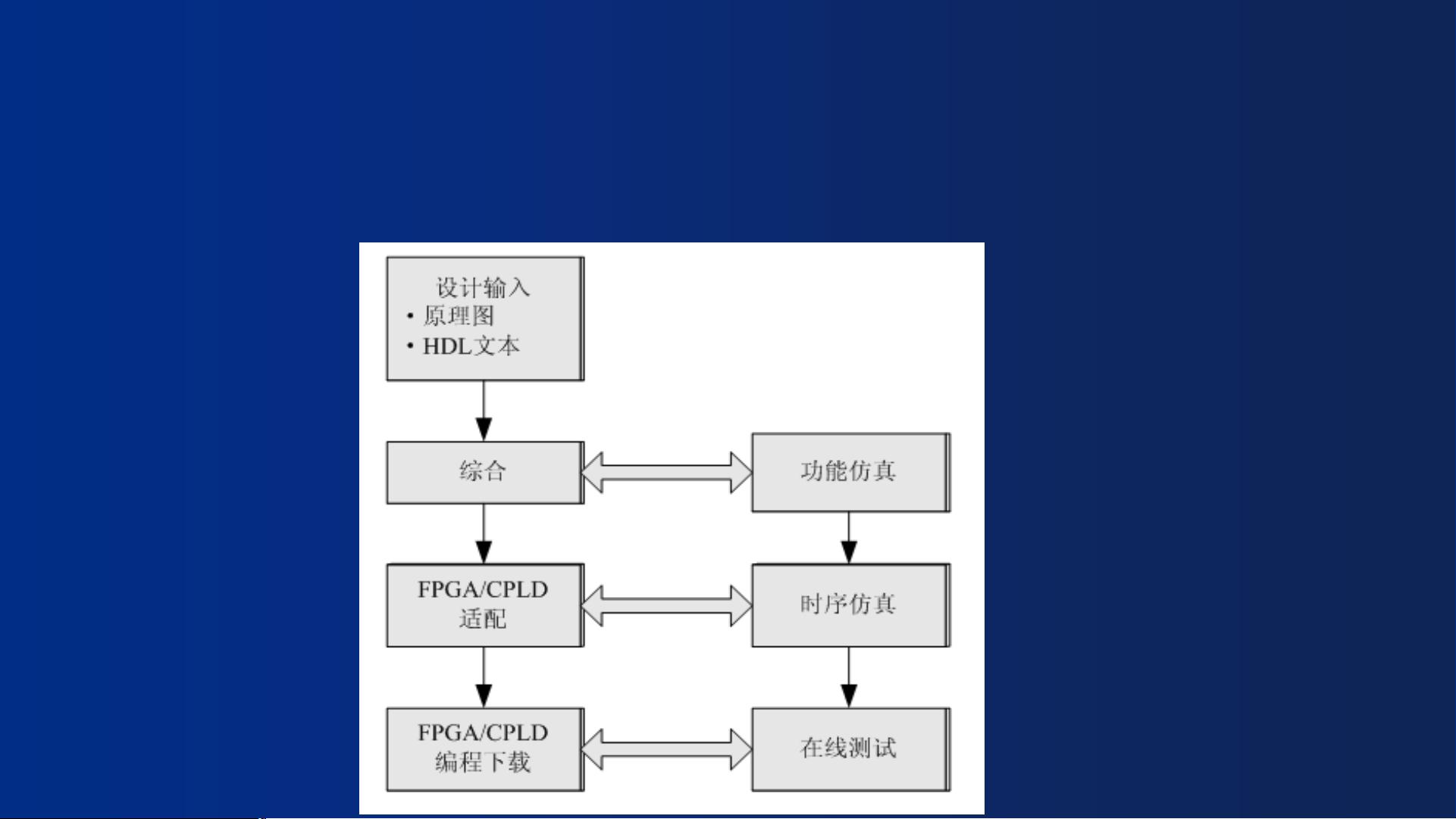

在这个PPT资源中,还介绍了EDA技术的概述和发展趋势。EDA技术是以计算机为工作平台,以EDA软件工具为开发环境,设计实现电路系统的一种技术。它将产品设计中具有高度重复性的繁杂劳动,如布图、布线工作等自动化,提高了设计效率和准确性。该资源对EDA技术的发展历程、Top-down设计与IP核复用、数字设计的流程和常用的EDA软件工具等进行了介绍。

总的来说,【考研复习资源】数字系统设计与Verilog HDL (第7版)PPT为读者提供了一份全面而详细的数字系统设计和Verilog HDL的教程。它是一份非常宝贵的考研复习资源,适合电子、计算机、自动化等相关专业的学生准备考研复习和自我学习使用。通过学习这个资源,读者能够掌握数字系统设计的核心知识和Verilog HDL的基础知识,提高自己在数字系统设计领域的能力。

149 浏览量

2021-10-08 上传

174 浏览量

119 浏览量

爱吃饼干的小白鼠

- 粉丝: 1w+

最新资源

- OctoPrint-TPLinkSmartplug插件的固件兼容性问题及解决方案

- Windows API系统托盘实例详解与交流指南

- Oracle EBS TRM技术参考手册解析

- 探索纯HTML5拓扑图编辑器源代码的无限可能

- ARKit实现裸手指空中绘画:Swift开发实战

- org.json JSONObject依赖的jar包及其版本号

- Bandicam 1.8.7.347:游戏录屏新选择,体积小音质佳

- MATLAB图像处理技术实现螺纹识别项目源代码

- 如何有效使用Window Installer Clean Up工具

- 聚合物Web组件简化D2L界面控制方法

- Tyra: 专为SEO优化的女性风格Gatsby启动器

- Windows NT 2000原生API参考手册下载

- 高效UDP日志传输:客户端与服务端代码实现

- 实现Android淡入淡出效果的欢迎界面教程

- uLog:嵌入式系统轻量级日志记录解决方案

- ARM裸奔环境下C库应用与Makefile实现指南