Vivado ECO实战:Tcl驱动的FPGA设计微调

100 浏览量

更新于2024-09-04

收藏 471KB PDF 举报

"Vivado使用误区与进阶——在Vivado中实现ECO功能"

在Vivado中,Engineering Change Order (ECO) 是一种在设计后期进行小范围修改的技术,它允许用户在不完全重新综合和布局布线的情况下,对已验证的设计进行快速调整。ECO在集成电路(IC)设计领域有悠久的历史,但在FPGA设计中相对较新。通过ECO,设计者可以尽量保留原有的功能和时序,以最小的成本和时间完成必要的改动。

ECO的常见应用场景包括但不限于:

1. 修改cell属性:当需要更新某个逻辑单元的配置参数时,ECO可以便捷地完成。

2. 增减或移动cell:在设计中添加或删除逻辑单元,或者改变它们的位置,而不会破坏整个设计的完整性。

3. 手动局部布线:对于特定的信号路径,可以通过ECO进行微调,优化信号质量或解决时序问题。

在Vivado中,ECO的实现并不像ISE工具那样提供一个独立的界面。相反,它需要利用Tcl脚本来进行。Vivado提供了丰富的Tcl命令集,使得用户能够对设计的多个方面进行精确控制。尽管一些简单的ECO操作可以通过图形用户界面完成,但更复杂的任务通常需要编写Tcl脚本来实现。

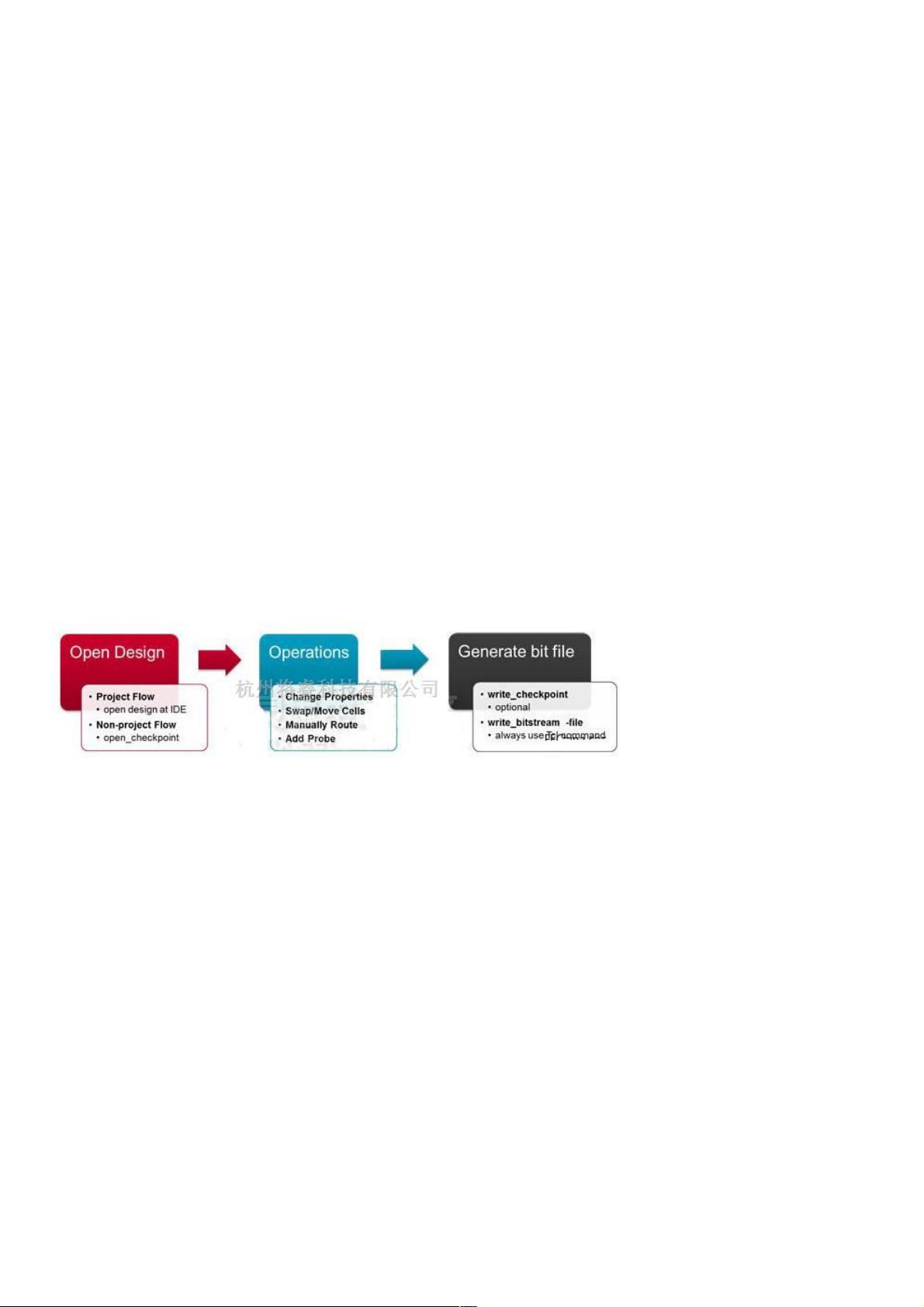

ECO的实现流程一般包括以下几个步骤:

1. 设计分析:首先,需要识别需要更改的部分,并评估这些更改对现有设计的影响。

2. ECO脚本编写:编写相应的Tcl脚本,指定要修改的元素,以及如何修改。

3. 验证更改:在执行ECO之前,通常会进行预后分析,以确认修改不会引入新的问题。

4. 应用ECO:运行Tcl脚本,对设计进行局部修改。

5. 后处理:更新约束,重新进行时序分析,确保设计仍然满足性能要求。

6. 仿真验证:最后,通过仿真确保修改后的设计功能正确并符合预期。

在实际操作中,Vivado的Design Manager和Tcl Console是进行ECO操作的主要工具。通过Design Manager,用户可以可视化地查看和编辑设计的不同层次;而Tcl Console则提供了强大的命令行接口,允许用户编写脚本,进行更复杂的自动化编辑。

Vivado中的ECO功能是高级FPGA设计中不可或缺的一部分,它提供了一种高效的方法来应对设计后期的微调需求。通过熟练掌握Tcl脚本和理解ECO的实施过程,设计者可以更灵活地处理设计变更,减少设计周期,提高产品上市速度。

2022-07-15 上传

2019-09-26 上传

2020-02-23 上传

2019-12-12 上传

2019-07-20 上传

119 浏览量

点击了解资源详情

点击了解资源详情

weixin_38508821

- 粉丝: 6

- 资源: 951

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器