ACEX1k SOPC开发板:嵌入式系统硬件平台

"ACEX_1k_SOPC_Development_Board 手冊"

这篇文档主要介绍了ACEX_1k_SOPC_Development_Board,这是一个用于ACEX 1k FPGA芯片上的系统级可编程片上开发板。该开发板包含了丰富的硬件资源,适合进行嵌入式系统的硬件开发和原型验证。

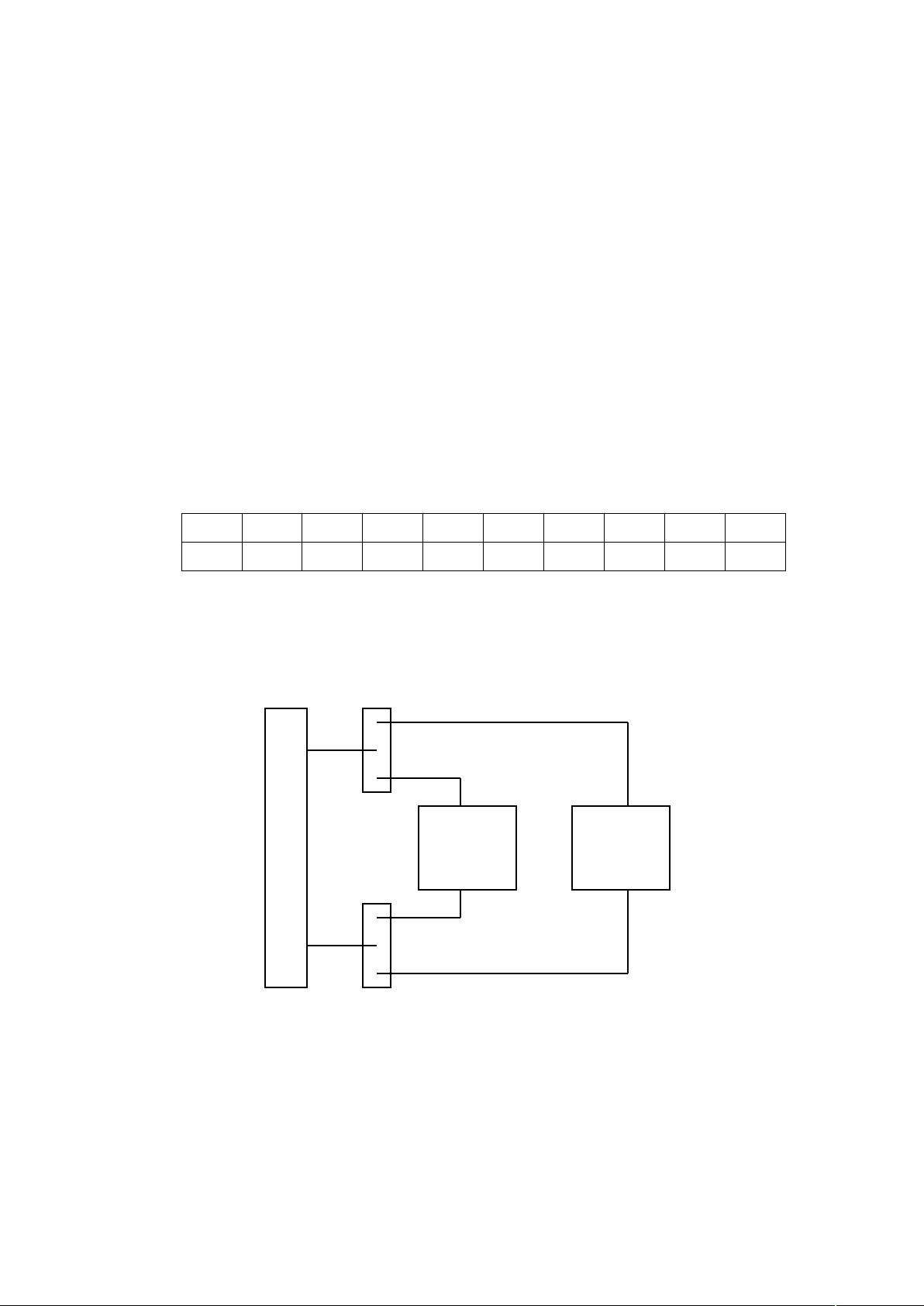

开发板的核心是ACEX1K100QC208-1芯片,这是一款拥有100,000个逻辑元件(LE)的FPGA,封装形式为PQFP,共有147个I/O脚位,工作电压为2.5V。它集成了4,992个可编程逻辑元素和49,152位的内部RAM。开发板提供了两种对ACEX芯片进行配置的方式:通过QuartusTM II软件利用ByteBlaster MV或MasterBlaster编程器通过JTAG接口(JP4)进行配置,或者在电源开启时由集成的配置控制器(U2)读取存在于Flash内存(U3)中的十六进制文件进行配置。

开发板上还配备了一个1M位(512×16-bits)的Flash内存芯片AM29LV800BB,该内存可以作为ACEX芯片内的Nios处理器的读写通用存储器,同时用于存储FPGA的配置文件。此外,开发板还包括了256K位的SRAM,一个RS-232串行接口,六个七段显示器,两个用户自定义的LED,四个用户定义的按键开关,一个八位拨动开关,以及一个用于ByteBlaster MV和MasterBlaster编程器的JTAG连接器。

这个开发板预装了32位的Nios嵌入式处理器系统参考设计,QuartusTM II项目目录中包含了相关的HDK(Hardware Development Kit)示例设计。在上电后,预加载到Flash中的参考设计和软件会自动启动,其中包括一个监视程序,可以用来下载和调试程序。

该开发板的独特之处在于其丰富的外设和预配置的Nios系统,使得开发者能够快速构建和测试基于ACEX 1k FPGA的嵌入式系统。通过结合硬件资源和软件工具,用户能够方便地进行系统级设计、逻辑验证和应用开发,大大简化了ACEX FPGA的学习和开发流程。对于想要学习FPGA设计,尤其是ACEX系列的工程师来说,这是一个理想的实践平台。

2013-05-15 上传

2020-07-27 上传

2020-12-08 上传

2021-09-25 上传

2020-12-13 上传

2013-05-15 上传

2007-10-11 上传

2010-05-06 上传

xyzgto

- 粉丝: 0

- 资源: 1

最新资源

- AA4MM开源软件:多建模与模拟耦合工具介绍

- Swagger实时生成器的探索与应用

- Swagger UI:Trunkit API 文档生成与交互指南

- 粉红色留言表单网页模板,简洁美观的HTML模板下载

- OWIN中间件集成BioID OAuth 2.0客户端指南

- 响应式黑色博客CSS模板及前端源码介绍

- Eclipse下使用AVR Dragon调试Arduino Uno ATmega328P项目

- UrlPerf-开源:简明性能测试器

- ConEmuPack 190623:Windows下的Linux Terminator式分屏工具

- 安卓系统工具:易语言开发的卸载预装软件工具更新

- Node.js 示例库:概念证明、测试与演示

- Wi-Fi红外发射器:NodeMCU版Alexa控制与实时反馈

- 易语言实现高效大文件字符串替换方法

- MATLAB光学仿真分析:波的干涉现象深入研究

- stdError中间件:简化服务器错误处理的工具

- Ruby环境下的Dynamiq客户端使用指南