FPGA驱动的高速CCD相机视频存储系统设计

184 浏览量

更新于2024-09-02

收藏 198KB PDF 举报

本文主要探讨了基于FAS466的高帧频、大面阵CCD相机数字视频实时存储系统的设计。随着这类CCD相机的广泛应用,其产生的图像数据量庞大,传统基于高性能计算机体系结构的存储方案,尽管实现相对简单,但由于依赖于PCI总线和受限于操作系统及文件系统的性能,存储速度往往无法达到理想的50MBps以上,难以满足高速实时记录的需求。

针对这个问题,作者提出了一种创新的设计思路,即设计一个脱离计算机平台的存储解决方案。该方案的核心是利用FPGA(Field-Programmable Gate Array)芯片,通过VHDL语言编程来实现对数据流的精确控制。FPGA作为可编程逻辑器件,可以灵活地配置和执行复杂的时序逻辑,这使得它能够克服总线瓶颈问题,同时减少对操作系统和文件系统的依赖,从而显著提升存储速率。

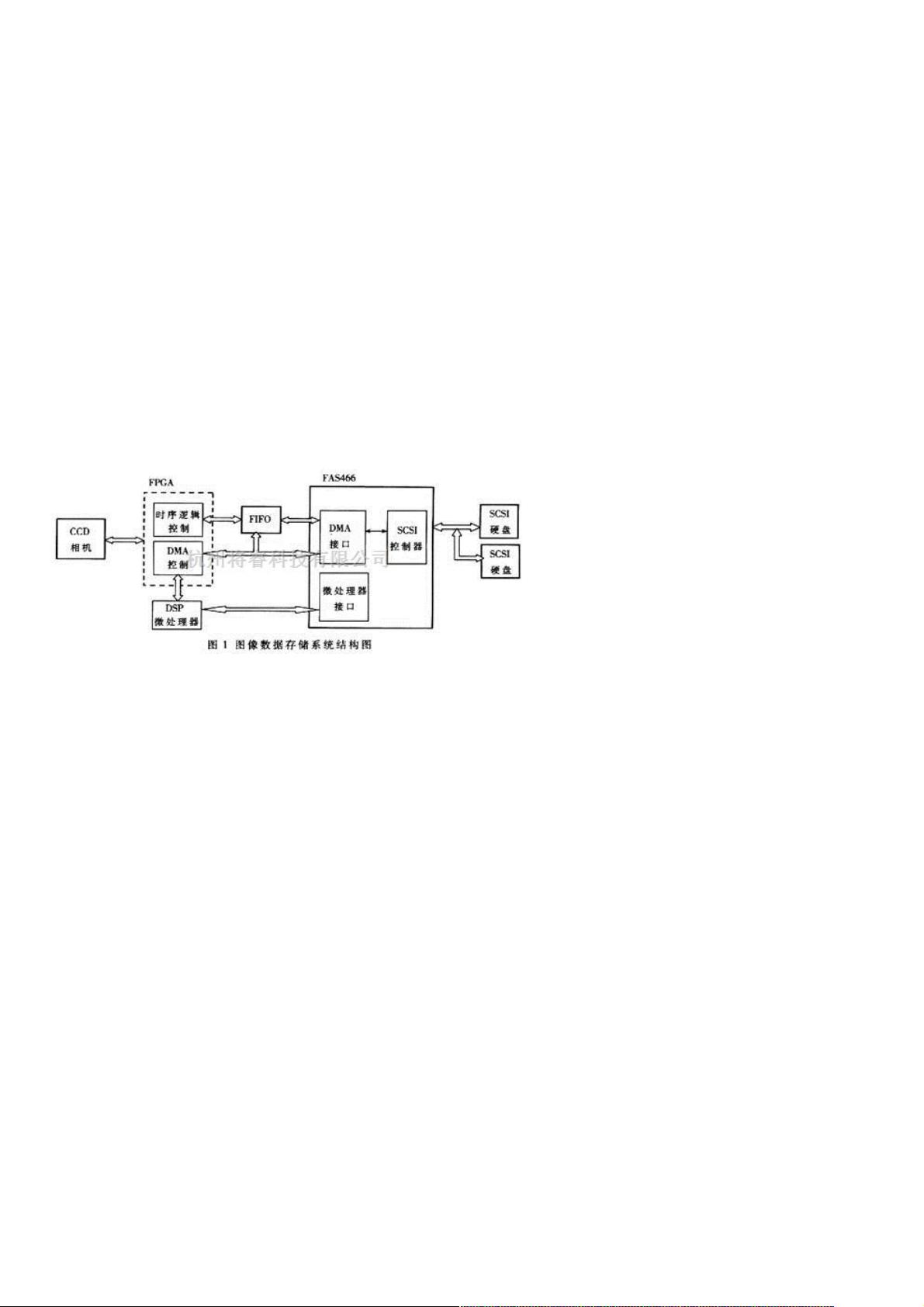

在硬件层面,这个系统包括了微处理器、DMA控制器、SCSI协议处理器以及数据缓存器等关键组件。微处理器,这里选择了高速的DSP(Digital Signal Processor),负责协调和控制整个系统的运行,如启动数据传输、对FPGA进行初始化、处理异常情况等。FPGA则承担起数据传输的调度和控制任务,通过VHDL编程实现了DMA控制功能,使得数据能够高效地通过SCSI协议处理器进行传输。

相比于传统的方案,FPGA的应用使得系统设计更为简洁,电路板体积减小,成本降低,且存储性能得到了显著提升。此外,图像数据存储系统结构图(图1)展示了各部分的连接和交互,直观地展示了这种新型设计的实施细节。

本文介绍的基于FAS466的CCD相机数字视频实时存储系统设计,不仅解决了高数据量和高速率存储的挑战,还展示了FPGA在硬件优化中的重要作用,为高性能视频监控和工业应用提供了新的可能。通过这样的设计,实际应用中的存储速度有望突破40MBps的限制,达到甚至超过50MBps的水平,这对于许多需要实时高清晰度视频数据采集的场景具有重要的实用价值。

2021-10-12 上传

2021-10-12 上传

2020-12-10 上传

2020-12-10 上传

2021-02-01 上传

2021-10-12 上传

2021-05-15 上传

2021-05-21 上传

2022-07-09 上传

Nedl002

- 粉丝: 148

- 资源: 947

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫