理解SDRAM:内存模组与时序解析

需积分: 9 173 浏览量

更新于2024-08-02

收藏 1.66MB PDF 举报

"SDRAM的原理和时序"

SDRAM(Synchronous Dynamic Random-Access Memory),同步动态随机存取内存,是计算机系统中常见的内存类型,它以系统时钟为基准进行数据传输,提高了数据处理速度。本文将深入探讨SDRAM的原理和时序。

一、SDRAM内存模组与基本结构

SDRAM通常以模组的形式存在,这是因为模组化设计能够更好地适应系统的需求。物理Bank(Physical Bank,P-Bank)是内存系统设计中的一个重要概念,它定义了内存与CPU数据总线之间的交互方式。P-Bank的位宽与CPU的数据总线位宽相匹配,确保CPU在一次传输周期内能接收所有所需数据。例如,早期的Pentium处理器需要64bit的数据总线,因此需要两条72pin-SIMM内存条来提供足够的位宽,而后来的168pin-SDRAM DIMM则可以单条满足这一需求。

二、芯片位宽

内存芯片的位宽决定了其一次传输的数据量。例如,16bit的芯片一次可以传输16bit数据,而8bit芯片则为8bit。为了达到P-Bank所需的64bit位宽,可能需要4颗16bit芯片或8颗8bit芯片并联工作。芯片位宽的选择受制于技术难度、成本和实际应用需求,通常不会设计得过大。

三、多Bank设计

随着计算机性能的提升,单个P-Bank无法满足大容量存储的需求,于是出现了多Bank设计。每个Bank都可以独立地进行读写操作,这样在访问不同Bank时可以重叠时序,提高内存系统的并发处理能力。例如,一个支持两个Bank的内存系统,当CPU在读取一个Bank的数据时,另一个Bank可以准备新的数据,从而提高了整体效率。

四、SDRAM的时序

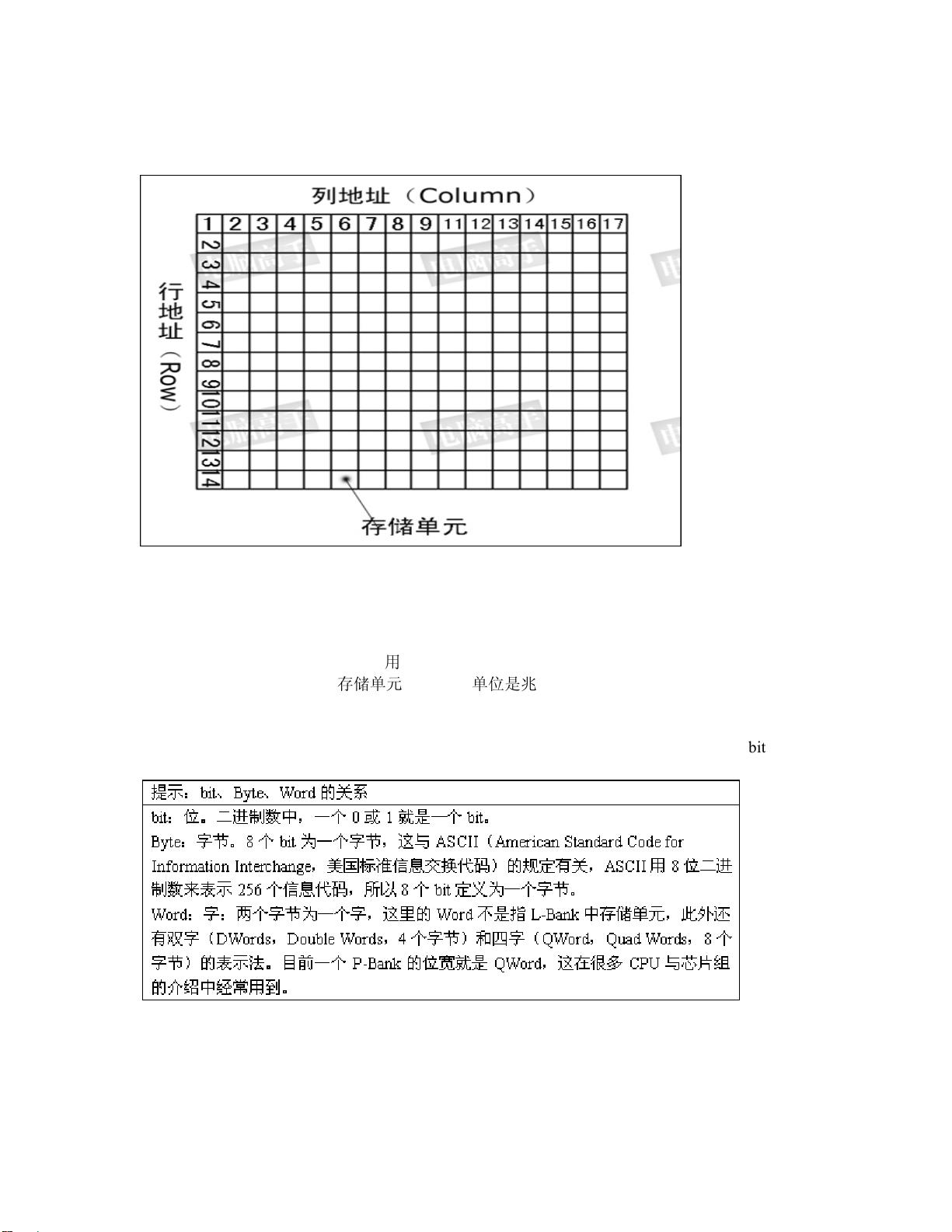

SDRAM的时序包括RAS(Row Address Strobe,行地址选通)、CAS(Column Address Strobe,列地址选通)和WR(Write,写入)等信号。RAS负责选择内存矩阵的行,CAS选择列,而WR则控制数据写入。这些信号的精确配合使得SDRAM能在指定时间内完成数据的读取和写入。此外,预充电(Precharge)操作用于关闭当前Bank并在下一个访问前准备Bank。

五、时钟周期与CAS延迟

SDRAM的工作依赖于系统时钟,每个时钟周期内可以执行特定的操作。CAS延迟(CAS Latency,CL)是指从CAS信号发出到数据有效出现在数据线上所需的时间,是衡量SDRAM性能的重要指标之一。较低的CAS延迟意味着更快的数据访问速度。

总结,SDRAM的原理在于通过物理Bank和芯片位宽的设计实现与CPU的高效通信,通过多Bank策略增加内存容量和并发性能,同时,复杂的时序控制确保了数据的准确传输。理解这些基础知识对于理解计算机内存系统的工作原理至关重要。

2010-01-14 上传

2013-07-31 上传

2023-07-09 上传

2023-05-12 上传

2023-08-17 上传

2023-04-28 上传

2023-03-28 上传

2023-07-14 上传

2024-01-20 上传

hfengyfan

- 粉丝: 0

- 资源: 3

最新资源

- 明日知道社区问答系统设计与实现-SSM框架java源码分享

- Unity3D粒子特效包:闪电效果体验报告

- Windows64位Python3.7安装Twisted库指南

- HTMLJS应用程序:多词典阿拉伯语词根检索

- 光纤通信课后习题答案解析及文件资源

- swdogen: 自动扫描源码生成 Swagger 文档的工具

- GD32F10系列芯片Keil IDE下载算法配置指南

- C++实现Emscripten版本的3D俄罗斯方块游戏

- 期末复习必备:全面数据结构课件资料

- WordPress媒体占位符插件:优化开发中的图像占位体验

- 完整扑克牌资源集-55张图片压缩包下载

- 开发轻量级时事通讯活动管理RESTful应用程序

- 长城特固618对讲机写频软件使用指南

- Memry粤语学习工具:开源应用助力记忆提升

- JMC 8.0.0版本发布,支持JDK 1.8及64位系统

- Python看图猜成语游戏源码发布