Serial ATA AHCI 1.1 Specification Revision 1_1.doc

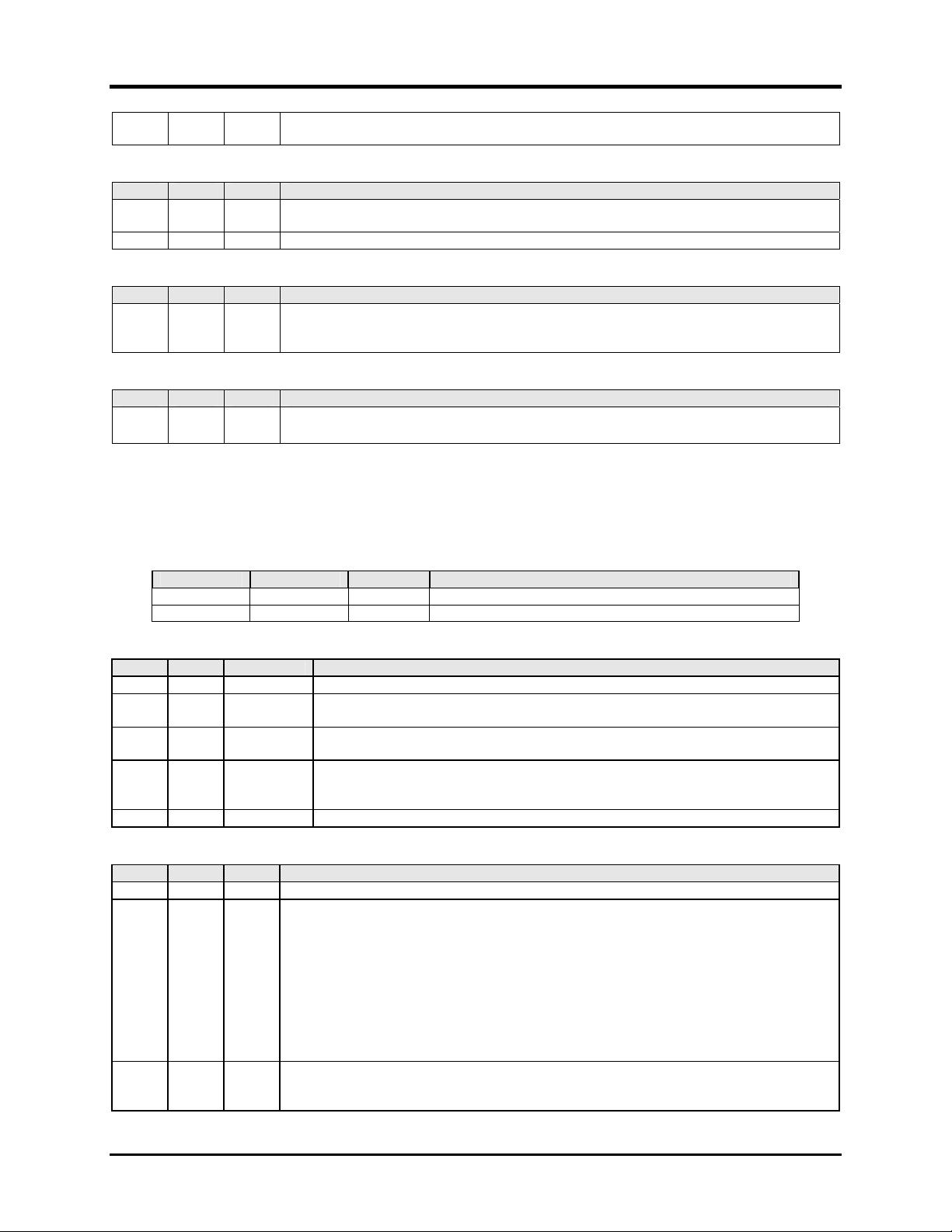

11

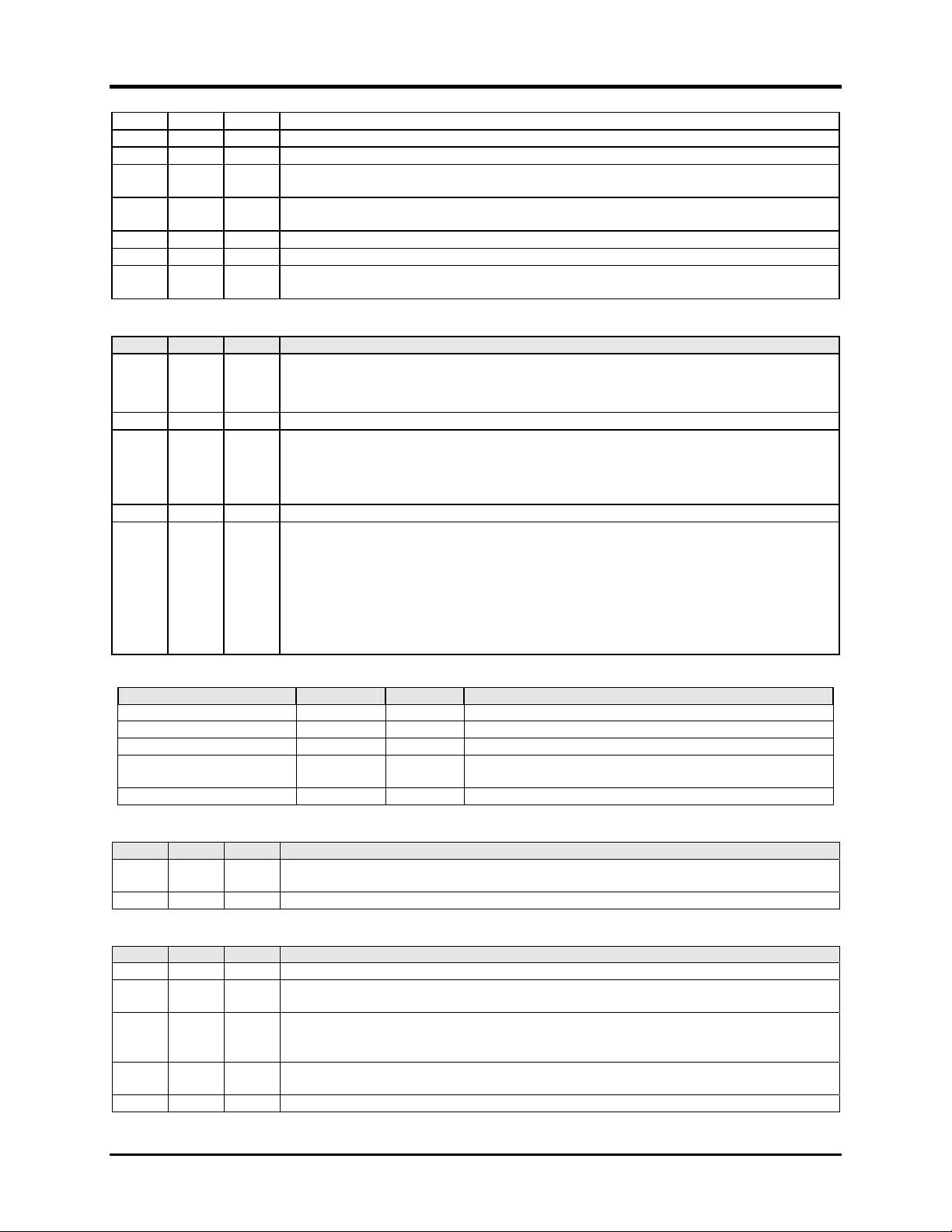

10 RO 0

D2_Support (D2S): The D2 state is not supported for AHCI HBAs.

09 RO 0

D1_Support (D1S): The D1 state is not supported for AHCI HBAs.

08:06 RO

Impl

Spec

Aux_Current (AUXC): Reports the maximum Suspend well current required when in

the D3

COLD

state. Refer to the PCI specification for definition of values.

05 RO

Impl

Spec

Device Specific Initialization (DSI): Indicates whether device-specific initialization is

required.

04 RO 0 Reserved

03 RO 0

PME Clock (PMEC): Indicates that PCI clock is not required to generate PME#.

02:00 RO

Impl

Spec

Version (VS): Indicates support for Revision 1.1 or higher revisions of the PCI Power

Management Specification.

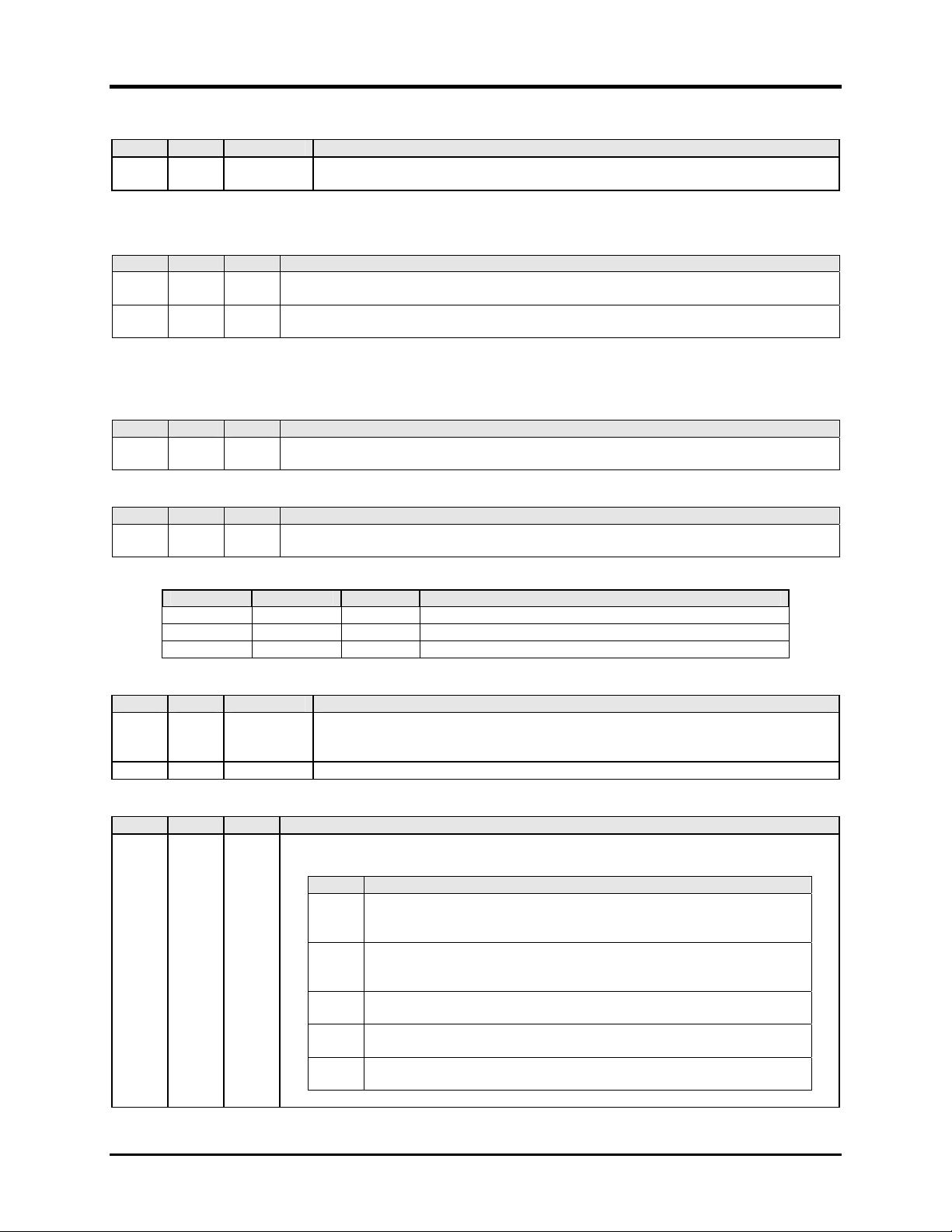

2.2.3 Offset PMCAP + 4h: PMCS – PCI Power Management Control And Status

Bit Type Reset Description

15 RWC

Impl

Spec

PME Status (PMES): Set to ‘1’ by hardware when the HBA generates PME#.

If the HBA supports waking from D3

COLD

, this bit is indeterminate at system boot. If the

HBA does not support waking from D3

COLD

, this bit is ‘0’ at system boot.

14:09 RO 0 Reserved – AHCI HBA does not implement the data register.

08 RW

Impl

Spec

PME Enable (PMEE): When set to ‘1’, the HBA asserts the PME# signal when PMES

is set to ‘1’.

If the HBA supports waking from D3

COLD

, this bit is indeterminate at system boot. If the

HBA does not support waking from D3

COLD

, this bit is ‘0’ at system boot.

07:02 RO 0 Reserved

01:00 R/W 00

Power State (PS): This field is used both to determine the current power state of the

HBA and to set a new power state. The values are:

00 – D0 state

11 – D3

HOT

state

The D1 and D2 states are not supported for AHCI HBAs. When in the D3

HOT

state, the

HBA’s configuration space is available, but the register memory spaces are not.

Additionally, interrupts are blocked.

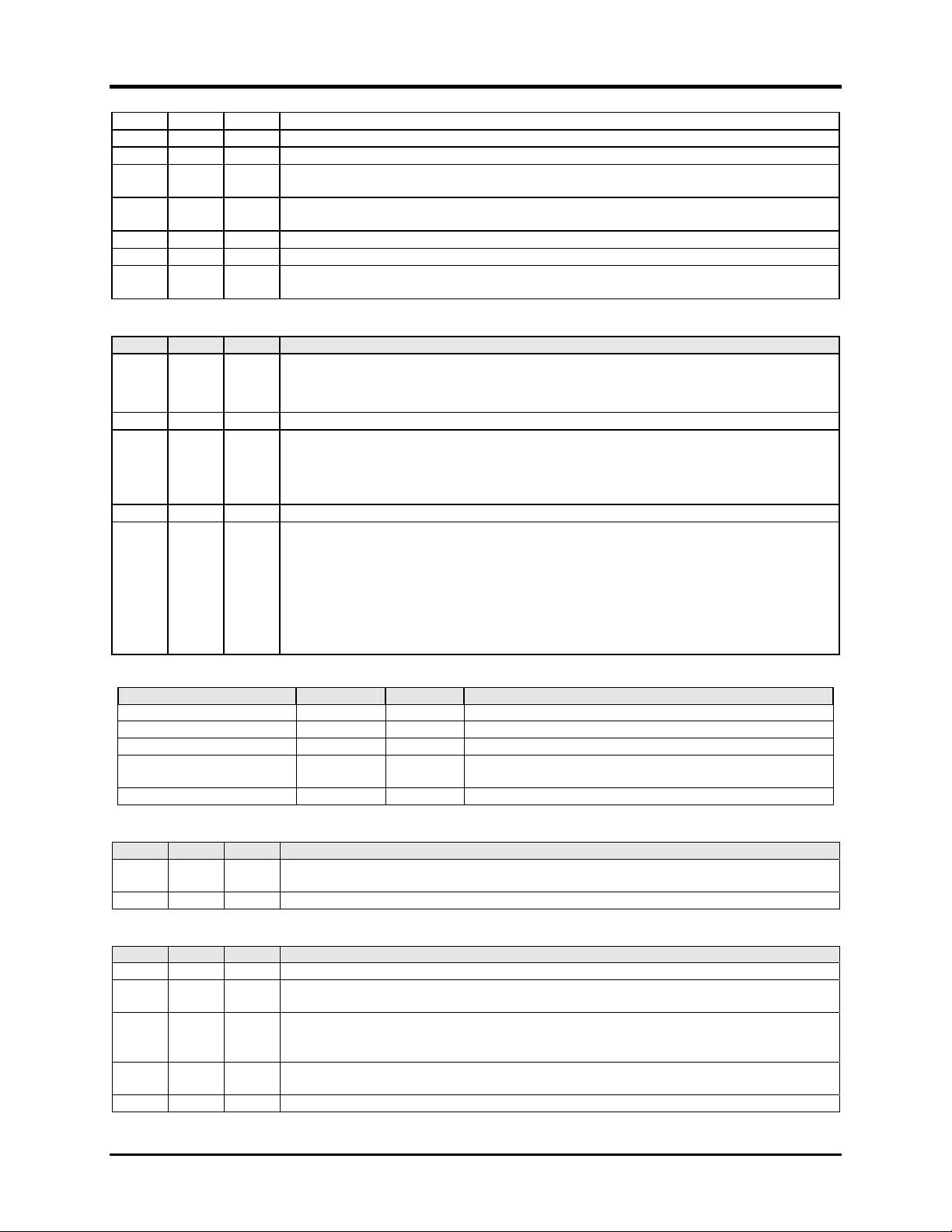

2.3 Message Signaled Interrupt Capability (Optional)

Start (hex) End (hex) Symbol Name

MSICAP MSICAP+1 MID Message Signaled Interrupt Capability ID

MSICAP+2 MSICAP+3 MC Message Signaled Interrupt Message Control

MSICAP+4 MSICAP+7 MA Message Signaled Interrupt Message Address

MSICAP+8 (MC.C64=0)

MSICAP+C (MC.C64=1)

MSICAP+9

MSICAP.D

MD Message Signaled Interrupt Message Data

MSICAP+8 (MC.C64=1) MSICAP+B MUA Message Signaled Interrupt Upper Address (Optional)

2.3.1 Offset MSICAP: MID – Message Signaled Interrupt Identifiers

Bits Type Reset Description

15:08 RO

Impl

Spec

Next Pointer (NEXT): Indicates the next item in the list. This can be other capability

pointers (such as PCI-X or PCI-Express) or it can be the last item in the list.

07:00 RO 05h

Capability ID (CID): Capabilities ID indicates MSI.

2.3.2 Offset MSICAP + 2h: MC – Message Signaled Interrupt Message Control

Bits Type Reset Description

15:08 RO 0 Reserved

07 RO

Impl

Spec

64 Bit Address Capable (C64): Specifies whether capable of generating 64-bit

messages.

06:04 RW 000

Multiple Message Enable (MME): Indicates the number of messages the HBA should

assert. See section 10.6.2.2. If the value programmed into this field exceeds the MMC

field in this register, the results are indeterminate.

03:01 RO

Impl

Spec

Multiple Message Capable (MMC): Indicates the number of messages the HBA

wishes to assert. See section 10.6.2.2.

00 RW 0

MSI Enable (MSIE): If set to ‘1’, MSI is enabled and the traditional interrupt pins are not