HI-6130, HI-6131

HOLT INTEGRATED CIRCUITS

16

2. FEATURE OVERVIEW

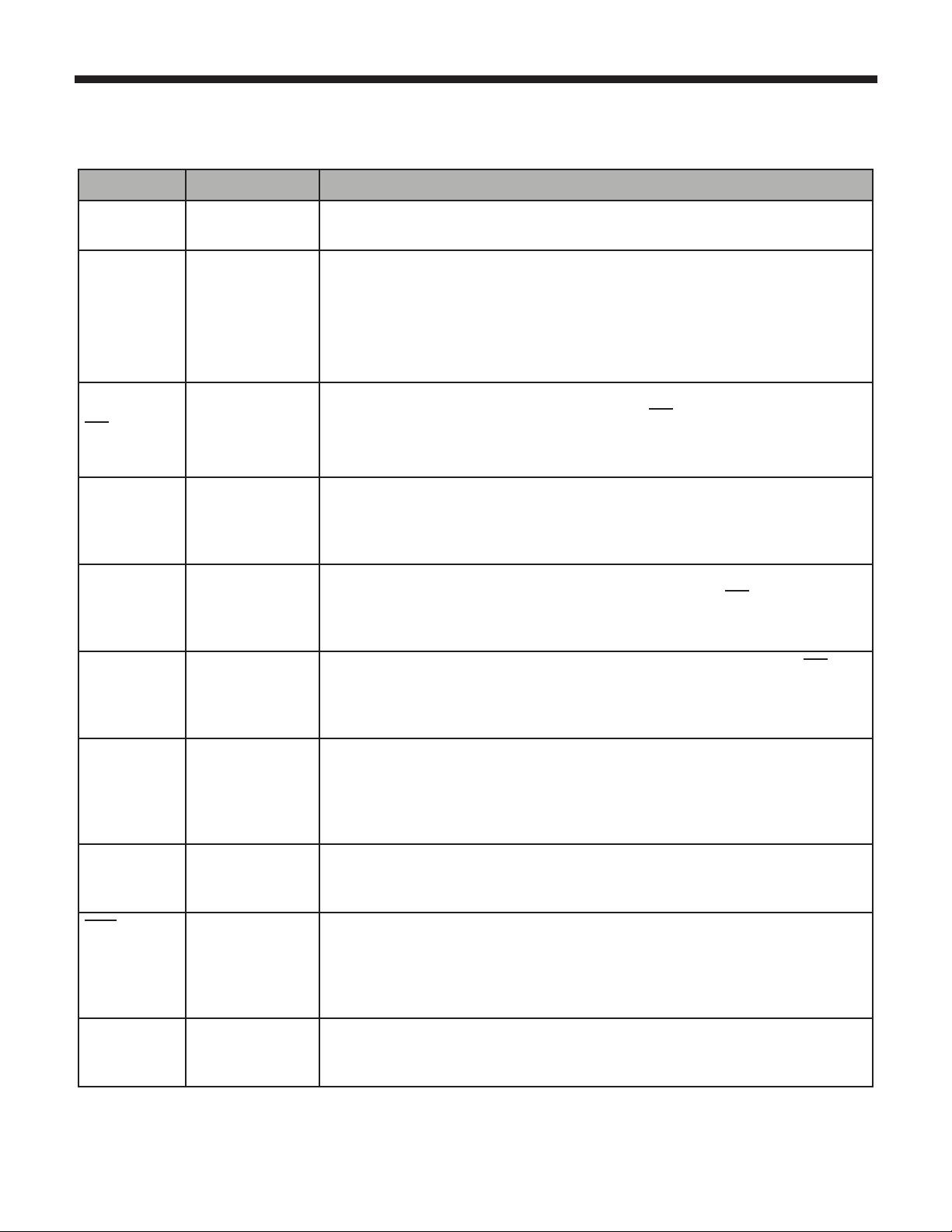

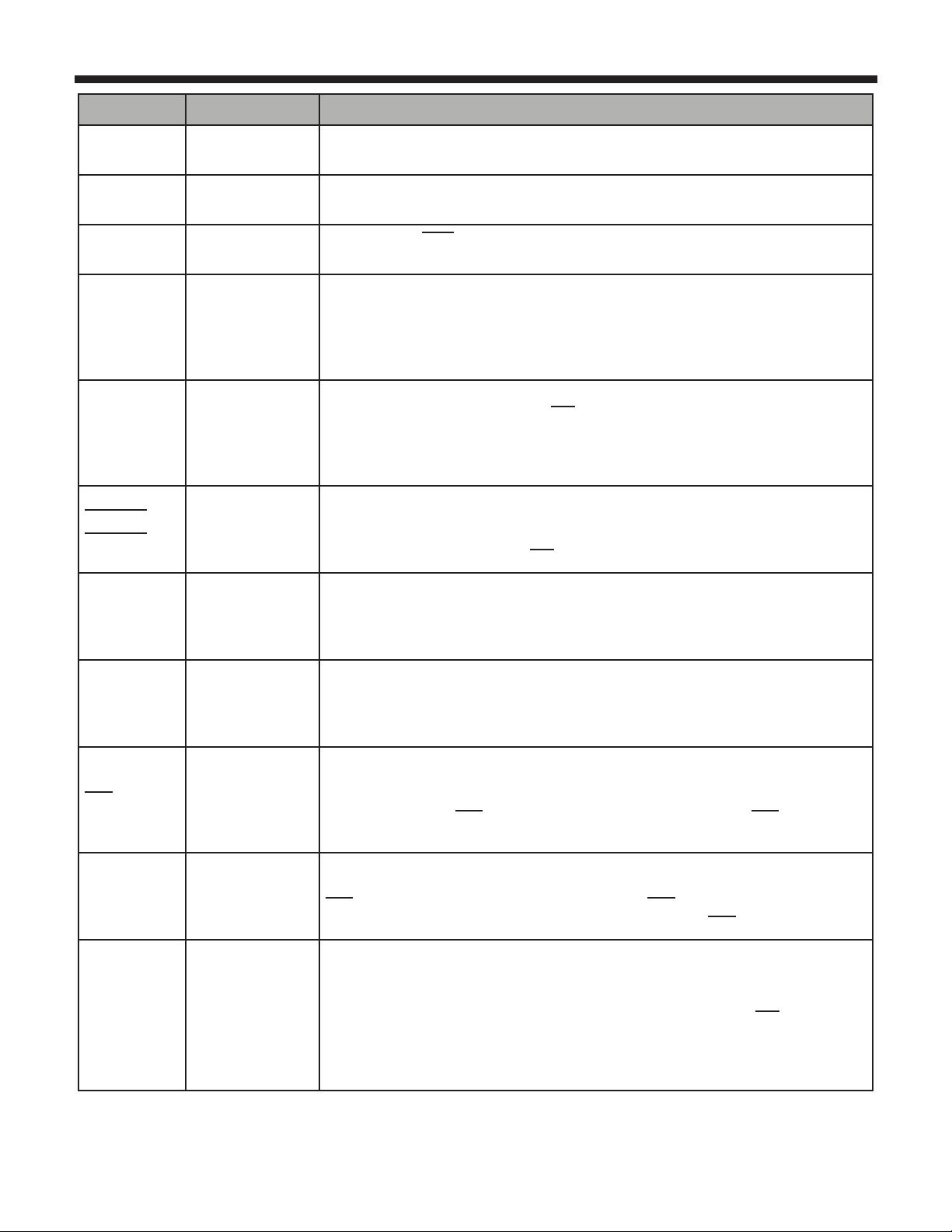

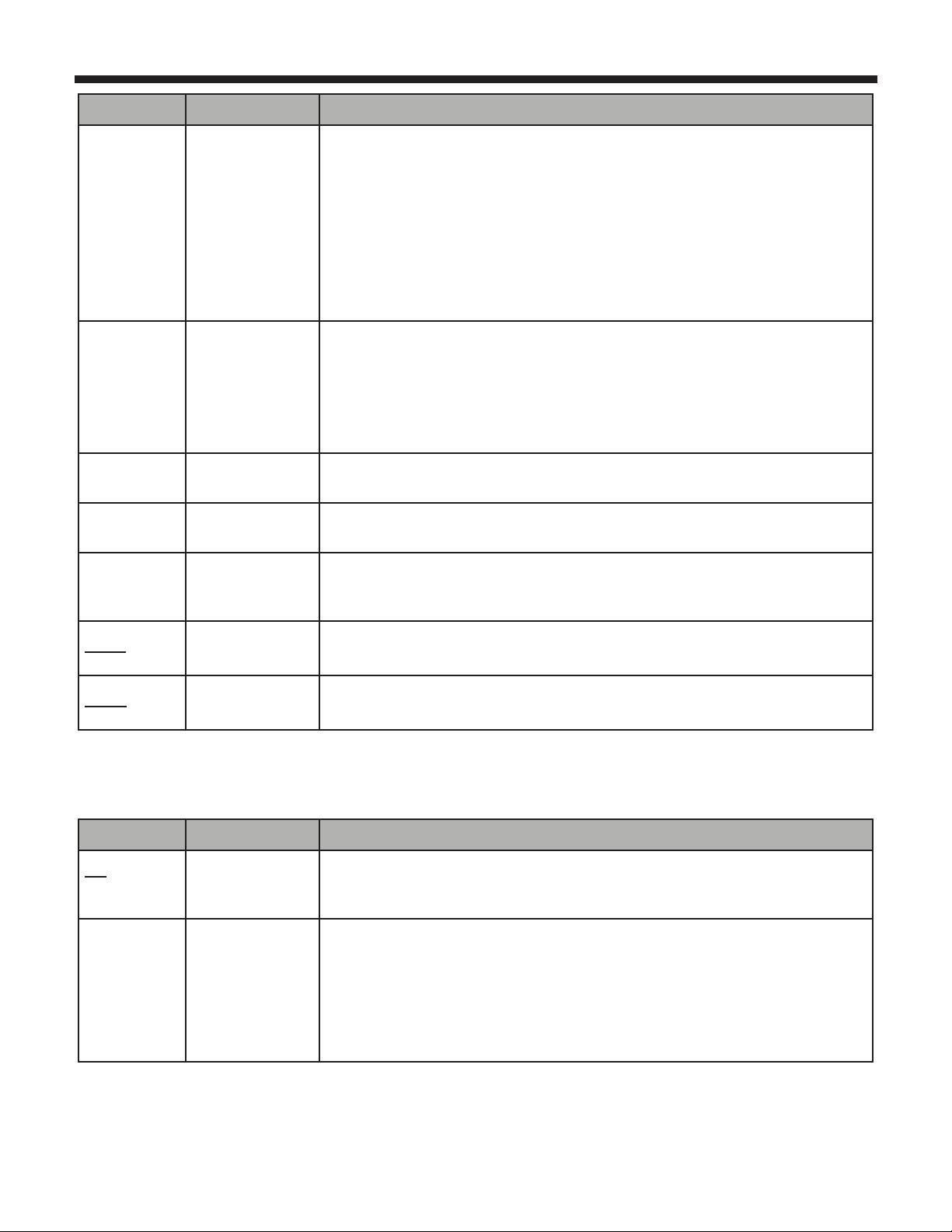

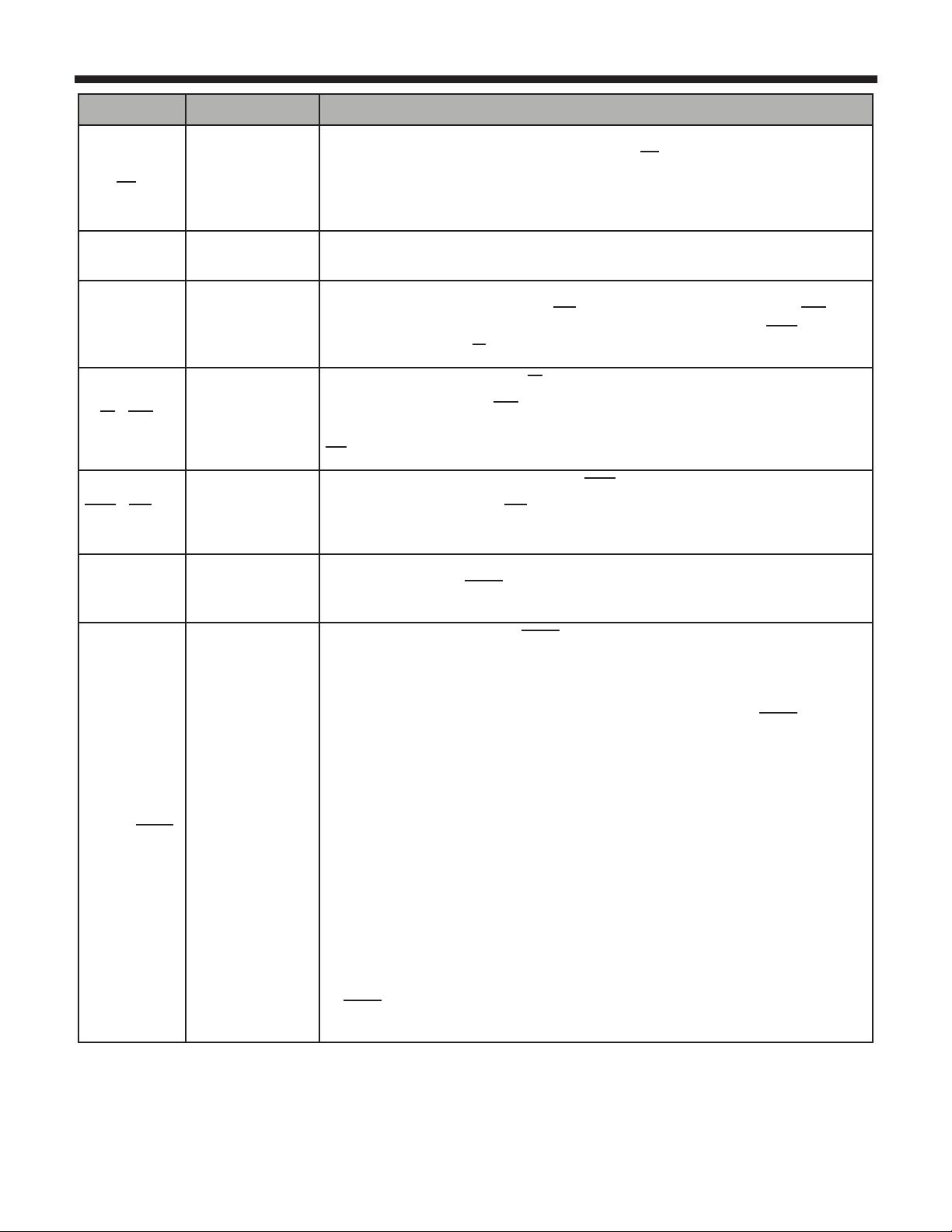

2.1. Bus Controller Operation

The HI-613x is congurable to operate as a Bus Controller

(BC). The BC is a programmable message-sequencing

device for control in MIL-STD-1553B applications.

Programmed using a set of 28 instruction op codes,

the BC greatly reduces the host’s processing workload.

The BC can optionally use a 16- or a 32-bit time base,

clocked from a choice of six internally generated clocks,

or an external time base clock. Special BC op codes

manage all 32-bit time base functions.

The programmable HI-613x Bus Controller autonomously

supports multi-frame message scheduling, message

retry schemes, storage of message data, asynchronous

message insertion and status /error reporting to the host

processor.

2.2. Remote Terminal Operation

The HI-613x is congurable to operate one as or two

Remote Terminals. The RTs are modeled after the popular

Holt HI-6120/21 Remote Terminal. The two Remote

Terminals operate with independent characteristics,

each RT having fully separate RAM structures (e.g.,

descriptor and illegal command tables) and independent

conguration and status registers. RAM buer options

include single, double and 2 circular buer choices. The

two RTs can be reset and reinitialized independently.

The full benet of two autonomous RTs is achieved

while using the same complexity and circuit board area

as a single Remote Terminal.

2.3. Monitor Terminal Operation

Message commands, terminal responses and message

data are stored in internal RAM, using one of two

possible modes. Simple Monitor Terminal (SMT) and

IRIG Monitor Terminal (IMT) Modes are targeted for

dierent applications. When operating in SMT mode, the

MT records commands and data separately. The SMT

can utilize 16- or 48-bit time tags with a range of clocking

options.

The IMT mode operation is designed to meet data

recording requirements of Telemetry Standard RCC

Document 106-07, Chapter 10. This “IRIG 106 Chapter

10” data recorder uses 48-bit relative time stamping,

having 10MHz (100ns) resolution. Message time stamps

occur at one of three selectable message progress

points. Several error handling schemes are available.

Bus Monitor interrupts notify the host when circular buer

rollover occurs, or when a user-programmed buer level

has been reached. The IMT stores message records

in the assigned buer using IRIG 106 “packet body”

format. The device can optionally generate complete

IRIG 106 packets, including full packet headers and

trailers meeting IRIG 106 Chapter 10 requirements.

2.4. Interrupts

Host interrupts can originate from device hardware or

any of the enabled terminal devices (up to 4 devices).

A circular 64-word Interrupt Log Buer retains interrupt

information from the last 32 interrupts, while the

hardware maintains a count of occurring interrupts since

the previous host buer service.

Hardware-assisted interrupt decoding provides quick

identication of the interrupt source by terminal device:

BC, MT, RT1, RT2 or hardware. When a hardware

interrupt occurs (e.g., Bus A Loopback Failure), a

Pending Hardware Interrupt register bit explicitly

identies the interrupt source. For interrupts from BC,

MT or RT, the three low-order bits in the same register

identify the specic interrupt register (or registers) with

pending interrupts: that is, the BC, MT or RT Pending

Interrupt registers.

2.5. Reset and Initialization

After hardware Master Reset, there are two HI-

613x initialization methods: host initialization or self-

initialization from external serial EEPROM. For host

initialization, the host processor uses its bus interface

or 4-wire SPI to load HI-613x registers and initialize

tables, data buers, etc. in internal static RAM. For self-

initialization, the device uses setup information contained

within an external serial EEPROM. A dedicated 4-wire

SPI port reads data from the serial EEPROM and writes

it to registers and RAM. Error checking is performed,

looking for data mismatch or an EEPROM checksum

error.

Individual 1553 terminal devices (BC, MT, RT1 or RT2)

can be re-initialized from the serial EEPROM by writing

to the Reset Initialization Register.