Verilog HDL高级教程:多时钟域、门控时钟与复位策略

需积分: 50 109 浏览量

更新于2024-07-28

收藏 1.02MB PPT 举报

Verilog HDL教程的高级篇深入探讨了多时钟域设计、门控时钟、同步与异步复位以及高速电路设计的相关概念和技术。在讲解中,作者首先强调了在实际的硬件设计中,多时钟域问题的处理至关重要,因为真实世界的电子系统通常涉及多个独立工作的时钟。时钟域指的是受特定时钟信号影响的电路区域,同步失败可能导致亚稳态状态,这涉及到寄存器的setup/hold时间规范。

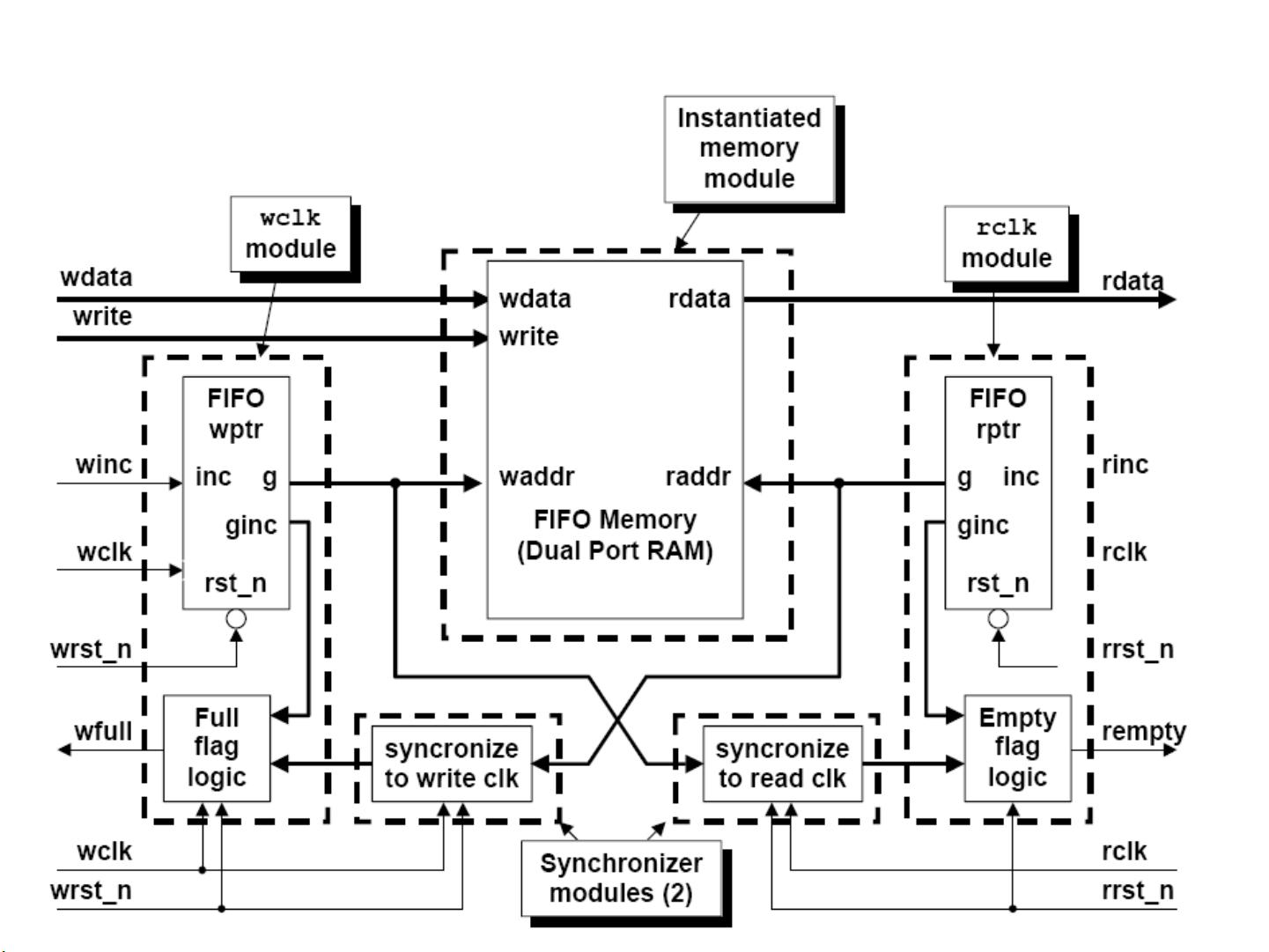

为解决时钟域间的同步问题,教程介绍了同步器在数据通路中的应用,包括握手信号、FIFO(先进先出队列)的双端口存储器设计,以及空闲/满状态的管理,如通过二进制或格雷计数器实现。设计一个优雅的解决方案需要考虑设计原则和编码风格,确保各个部分之间的协调。

门控时钟(Gated clock)作为一种技术,能够提高电路速度、减少面积并降低功耗,但它对工具支持要求较高。GCK单元的使用需谨慎对待,特别是要关注GATE和CLK之间的异步行为以及可能存在的毛刺问题,可以通过latch来避免这些问题。

复位功能在电路设计中扮演关键角色,它帮助系统恢复到预设状态。同步复位具有优点,如100%同步设计和时钟消除毛刺的能力,但需要额外的同步机制来确保复位信号被正确采样。反之,异步复位无需额外逻辑,适用于无时钟或低时钟频率的情况,但可能会引入额外的复杂性,比如复位延迟和潜在的毛刺问题。

在实践中,设计者需要根据具体应用场景和性能需求,灵活运用这些技术,权衡同步与异步复位的优缺点,以实现高效、稳定和可靠的电路设计。此外,练习环节提供了使用Verilog HDL描述两级同步器的机会,让学生能够在实际项目中应用所学知识。

2009-03-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

qiuwenwei105240

- 粉丝: 4

- 资源: 44

最新资源

- 开源通讯录备份系统项目,易于复刻与扩展

- 探索NX二次开发:UF_DRF_ask_id_symbol_geometry函数详解

- Vuex使用教程:详细资料包解析与实践

- 汉印A300蓝牙打印机安卓App开发教程与资源

- kkFileView 4.4.0-beta版:Windows下的解压缩文件预览器

- ChatGPT对战Bard:一场AI的深度测评与比较

- 稳定版MySQL连接Java的驱动包MySQL Connector/J 5.1.38发布

- Zabbix监控系统离线安装包下载指南

- JavaScript Promise代码解析与应用

- 基于JAVA和SQL的离散数学题库管理系统开发与应用

- 竞赛项目申报系统:SpringBoot与Vue.js结合毕业设计

- JAVA+SQL打造离散数学题库管理系统:源代码与文档全览

- C#代码实现装箱与转换的详细解析

- 利用ChatGPT深入了解行业的快速方法论

- C语言链表操作实战解析与代码示例

- 大学生选修选课系统设计与实现:源码及数据库架构