Vivado FPGA设计入门:从零开始的开发流程

需积分: 48 64 浏览量

更新于2024-07-08

1

收藏 1.76MB PDF 举报

"vivado基本开发流程.pdf"

Vivado是一款强大的FPGA(Field Programmable Gate Array)设计工具,由Xilinx公司提供,用于实现从逻辑设计到硬件实现的全流程。对于FPGA初学者而言,掌握Vivado的基本开发流程至关重要。以下将详细解析这一流程:

1. 启动Vivado

Vivado可以通过桌面快捷方式或从开始菜单启动。快捷键启动是直接双击安装后的桌面图标;从开始菜单启动,需进入Xilinx Design Tools目录下的相应版本。

2. 创建FPGA设计工程

- 打开Vivado,用户将看到启动界面,其中包含QuickStart、Tasks和Learning Center三个部分。QuickStart组有创建新项目、打开项目和打开示例项目等选项。

- 要创建新工程,点击QuickStart组中的“Create Project”。这将引导用户通过向导一步步设置工程。

3. 设置工程属性

- 在“Create a New Vivado Project”对话框中,输入工程名和路径。确保选择“Create project subdirectory”,并避免在路径和名称中使用空格或中文字符,以防止后续出错。

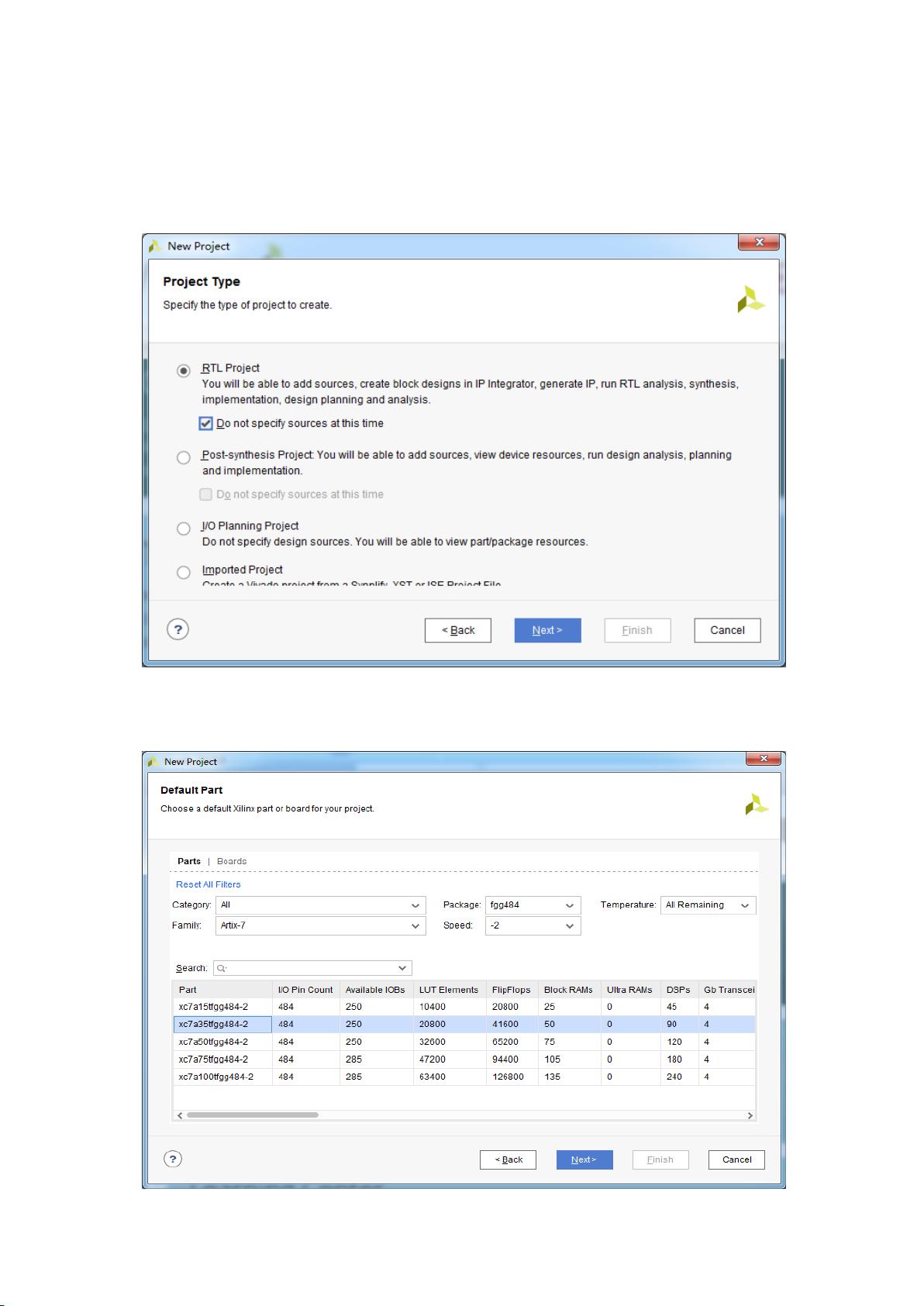

4. 选择工程类型

- 在“Project Type”对话框中,用户可以选择不同的工程类型,如RTL工程,这是最常用的一种,适合于描述设计的逻辑行为。

5. 选择目标设备

- 接下来,用户需要指定目标FPGA器件,这将决定设计能够运行在哪种硬件平台上。

6. 添加源文件

- 在工程创建后,用户需要添加源文件,包括Verilog或VHDL等硬件描述语言文件,这些文件包含了FPGA设计的具体逻辑。

7. RTL描述与分析

- RTL(Register Transfer Level)描述是FPGA设计的核心,它定义了数据如何在硬件寄存器之间流动。Vivado提供了设计编辑器,用于编写和检查RTL代码。

8. 设计综合

- 综合阶段是将RTL代码转换成门级网表的过程,Vivado自动完成此过程,优化逻辑以适应选定的FPGA架构。

9. 添加设计约束

- 在设计综合之前,需要添加时序约束,以规定设计中各部分的延迟要求,确保系统满足实时性需求。

10. 设计实现

- 实现阶段是将综合后的网表映射到FPGA的逻辑单元和布线资源上,Vivado会进行布局和布线,以达到最佳性能。

11. 比特流文件生成

- 完成设计实现后,Vivado会生成一个.bit文件,即比特流文件,它是FPGA配置的数据文件。

12. 下载比特流文件

- 比特流文件需要下载到FPGA硬件中,以实现设计的功能。这通常通过硬件管理器完成,连接FPGA板卡并加载比特流。

13. BIN文件生成与固化

- BIN文件是一种二进制文件,用于某些FPGA的配置,它可以被烧录到非易失性存储器中,使得FPGA在每次上电时自动加载配置。

以上就是Vivado的基本开发流程,涵盖了从工程创建到硬件验证的全过程。学习和掌握这个流程对于理解和应用FPGA技术至关重要。在整个过程中,Vivado提供了丰富的工具和向导,帮助用户有效地进行设计和调试。

2021-06-22 上传

2020-04-10 上传

2021-07-26 上传

2020-03-06 上传

2021-01-21 上传

2021-09-13 上传

2020-11-16 上传

射手Snake357

- 粉丝: 1

- 资源: 12

最新资源

- 过滤器返冲洗控制程序.rar

- mod5

- ImgHosting:图片托管

- 云原生架构白皮书.zip

- 行业文档-设计装置-一种可充气变形省空的书架.zip

- TPFinal_IngSoftware2020_UCEL:在Web的Aportes Tecso仓库创建证书,在UCEL的Ingenieria软件工程2020版最终发布

- LP2

- node-sqs-processor:SQS队列处理模块

- 三系列浓相输送监控系统设计与实现

- Accuinsight-1.0.35-py2.py3-none-any.whl.zip

- node-servoblaster:用于 Node.js 的 ServoBlaster 库

- fb41源程序.rar

- git-json-api:通过HTTP从Git存储库中的JSON文件中获取内容(以及POST更改)

- 调试

- assignment

- weixin052用于日语词汇学习的微信小程序+ssm后端毕业源码案例设计