Cadence设计系统:学习与应用详解

需积分: 10 32 浏览量

更新于2024-08-02

收藏 3.63MB PPT 举报

"Cadence设计系统是集成电路设计中广泛使用的电子设计自动化(EDA)工具,尤其在微电子领域有重要应用。该系统包括了多个关键组件,如版图设计工具Virtuoso LE、版图验证工具Diva和Dracula等。Cadence设计流程覆盖了从设计初期的概念到最终的制造,涉及到了电路仿真、逻辑综合、可测性设计和低功耗设计等多个环节。随着集成电路技术的发展,特征尺寸不断减小,对设计工具的要求也越来越高,Cadence作为强大的EDA工具,对于应对设计复杂度的提升至关重要。"

在半导体行业中,Cadence设计系统扮演着核心角色,它是由Cadence公司开发的一套全面的集成化设计解决方案。Cadence系统主要包括以下几个方面:

1. **Cadence系统概述**:Cadence设计系统涵盖了整个集成电路设计流程,包括前端设计(如VHDL仿真和行为综合)和后端设计(如版图设计和验证)。系统启动和帮助系统为用户提供便捷的使用体验。

2. **版图设计工具-Virtuoso LE**:Virtuoso是一款高级的模拟和混合信号设计平台,它支持复杂IC设计的版图编辑和优化,提供了一流的设计环境,允许工程师在纳米级别进行精确的布局和布线。

3. **版图验证工具**:Diva和Dracula是用于验证版图是否符合设计规则和电气规则的工具,确保版图的正确性和功能性,防止潜在的制造问题。

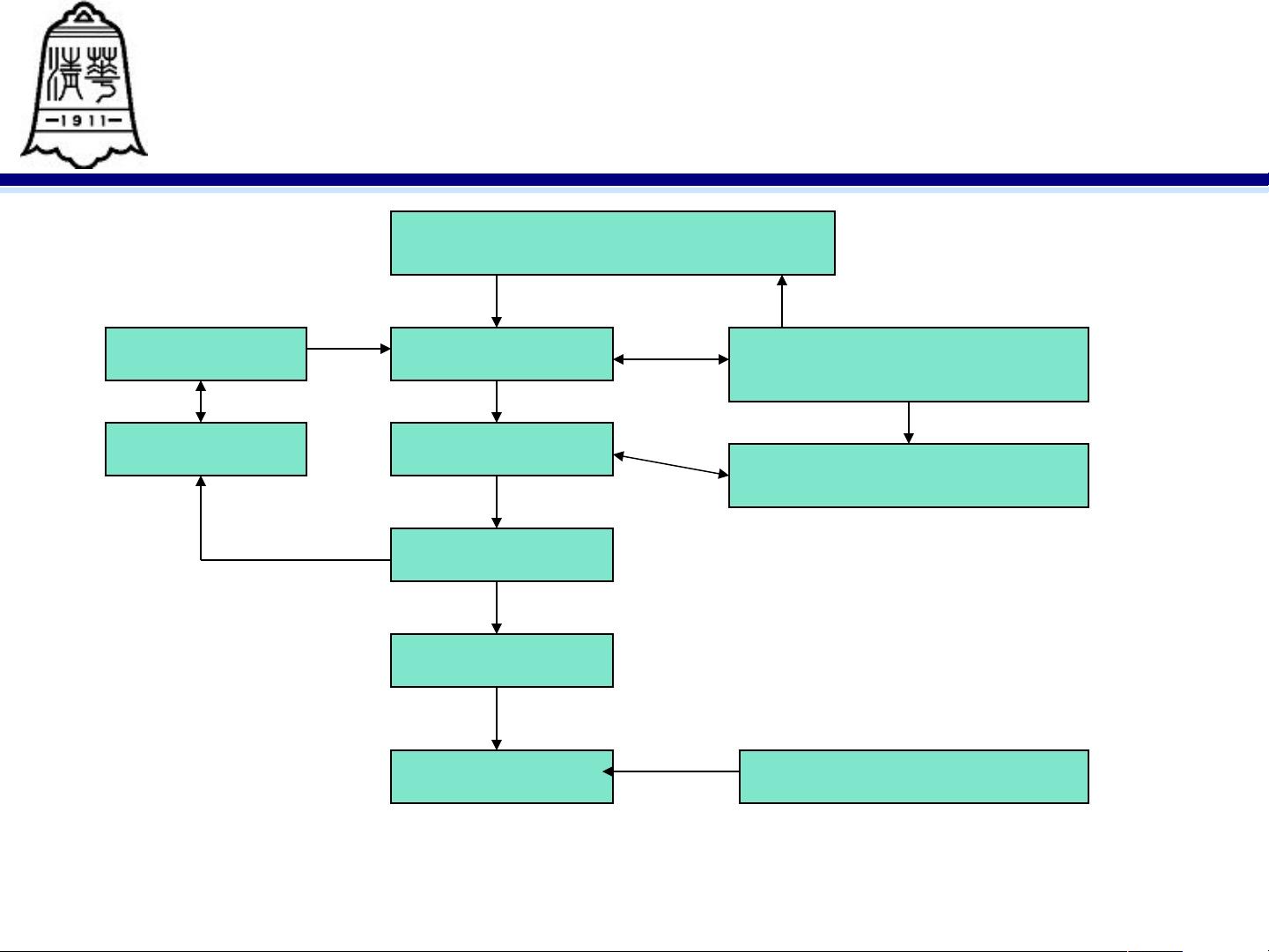

4. **设计流程**:Cadence设计流程反映了集成电路设计的各个阶段,包括功能验证、逻辑综合、物理实现、布局布线以及功耗分析等,确保设计满足性能、功耗和面积(PPA)的目标。

5. **市场需求与工艺技术发展**:随着集成电路技术的快速发展,特征尺寸不断缩小,电源电压降低,晶体管数量大幅增加,这导致设计复杂度急剧上升。Cadence工具通过提供先进的设计和验证手段,帮助工程师应对这些挑战。

6. **VHDL仿真**:VHDL是一种硬件描述语言,用于描述数字系统的逻辑功能。Cadence支持VHDL仿真是为了验证设计行为是否符合预期,确保其在实际运行时的正确性。

7. **低功耗设计**:随着便携式和桌面产品的功耗要求越来越严格,Cadence系统提供了低功耗设计工具和方法学,帮助设计师优化设计以减少能量消耗。

Cadence设计系统是现代集成电路设计不可或缺的一部分,它提供的强大功能和高效工具,使得设计师能够应对日益复杂的IC设计任务,推动了微电子行业的创新和发展。

101 浏览量

2193 浏览量

2021-10-07 上传

2024-11-11 上传

2024-11-11 上传

2024-11-03 上传

2024-11-04 上传

2024-11-04 上传

180 浏览量

jsjhxh

- 粉丝: 5

- 资源: 33