TMS320C5x, TMS320LC5x

DIGITAL SIGNAL PROCESSORS

SPRS030A – APRIL 1995 – REVISED APRIL 1996

18

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

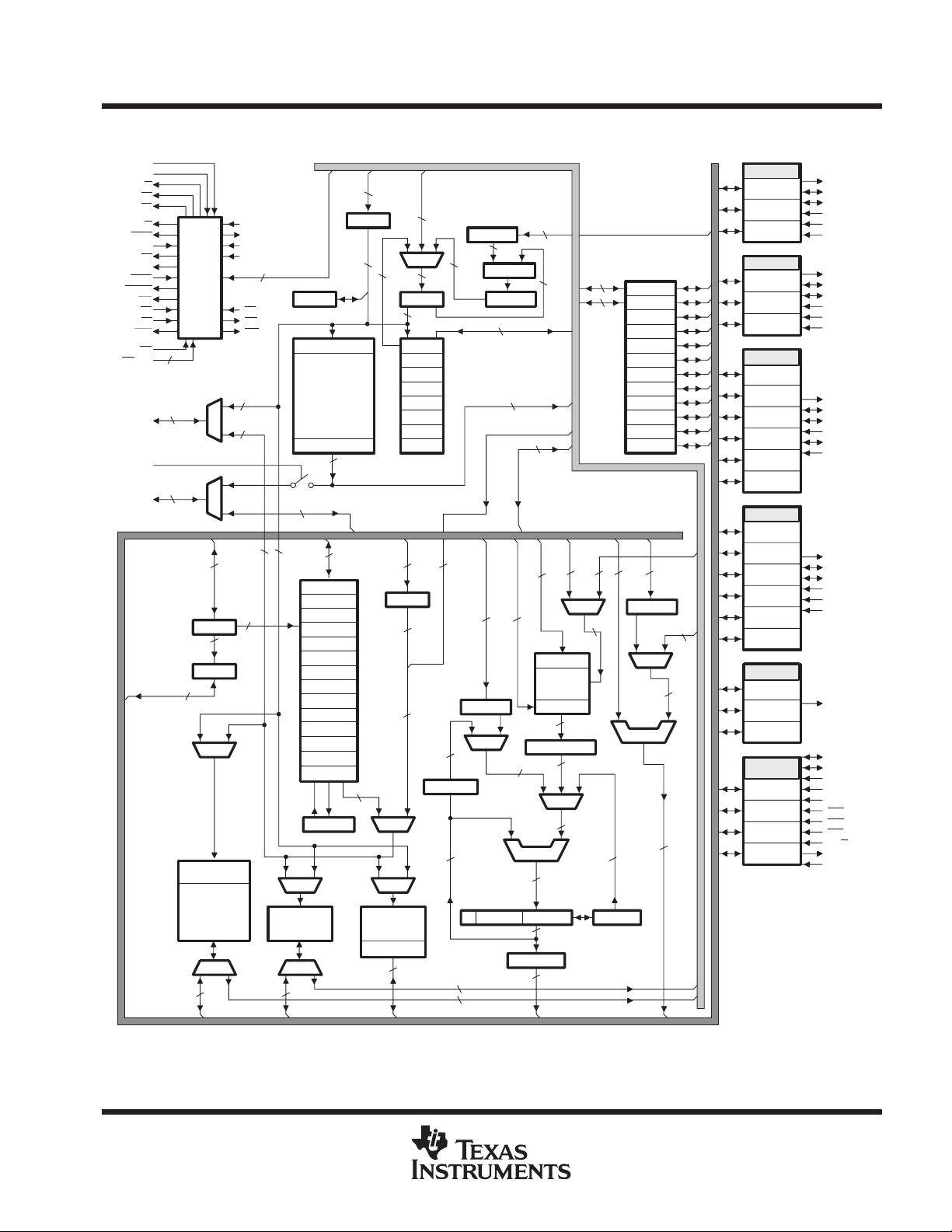

architecture

The ’C5x’s advanced Harvard-type architecture maximizes the processing power by maintaining two separate

memory bus structures, program and data, for full-speed execution. Instructions support data transfers between

the two spaces. This architecture permits coefficients stored in program memory to be read into the RAM,

eliminating the need for a separate coefficient ROM. The ’C5x architecture also makes available immediate

instructions and subroutines based on computed values. Increased throughput on the ’C5x for many DSP

applications is accomplished using single-cycle multiply/accumulate instructions with a data-move option, up

to eight auxiliary registers with a dedicated arithmetic unit, a parallel logic unit, and faster I/O necessary for

data-intensive signal processing. The architectural design emphasizes overall speed, communication, and

flexibility in processor configuration. Control signals and instructions provide floating-point support,

block-memory transfers, communication to slower off-chip devices, and multiprocessing implementations

as shown in the functional block diagram.

Table 3 explains the symbols that are used in the functional block diagram.

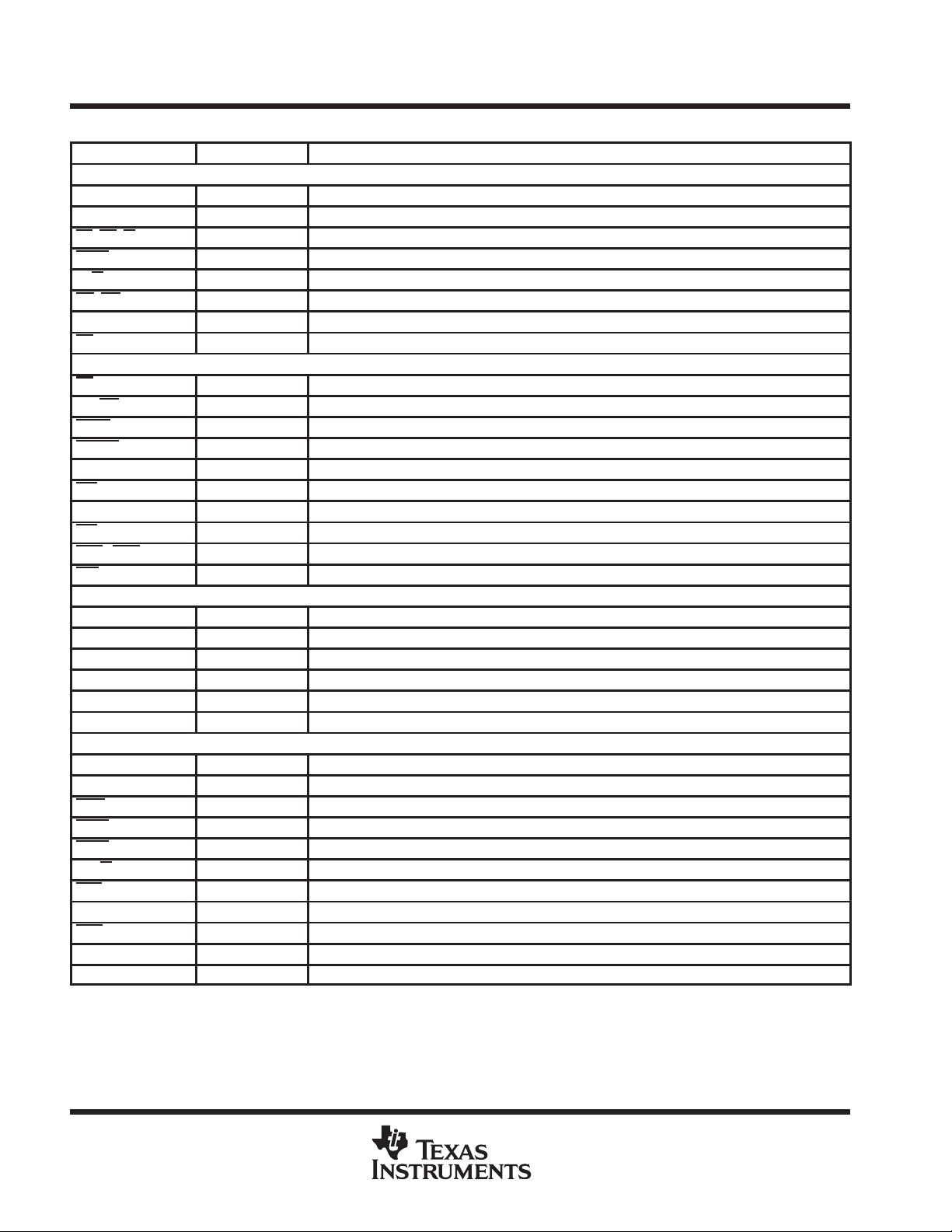

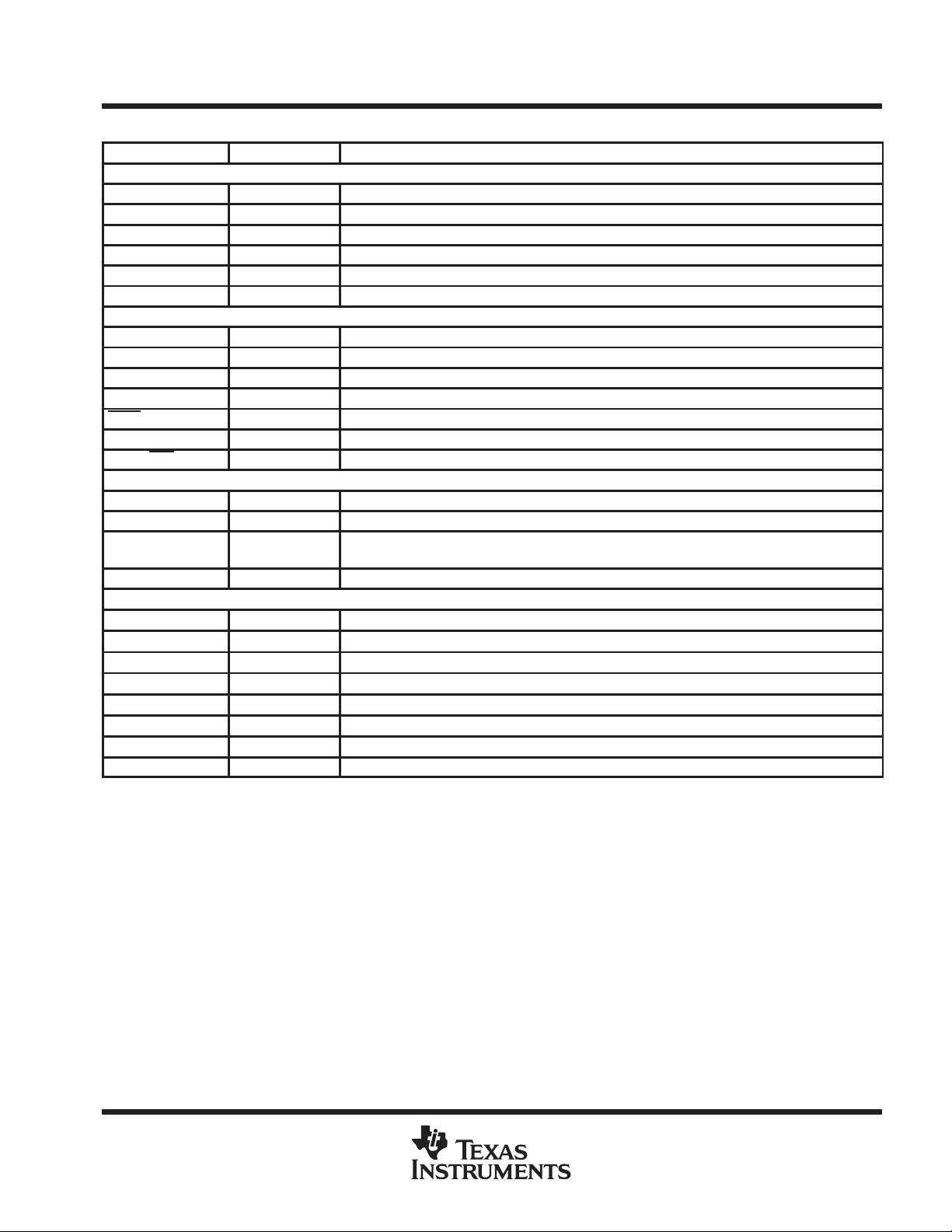

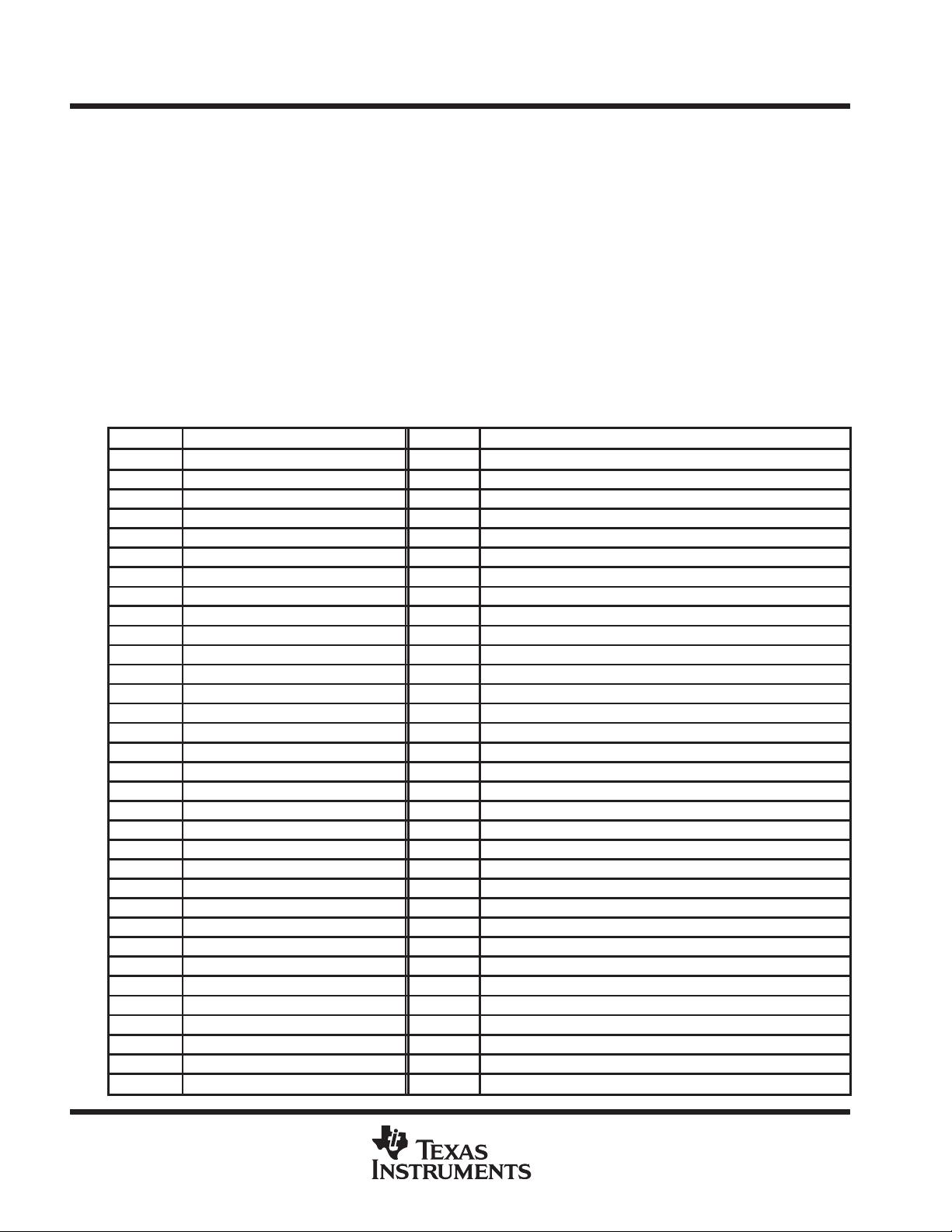

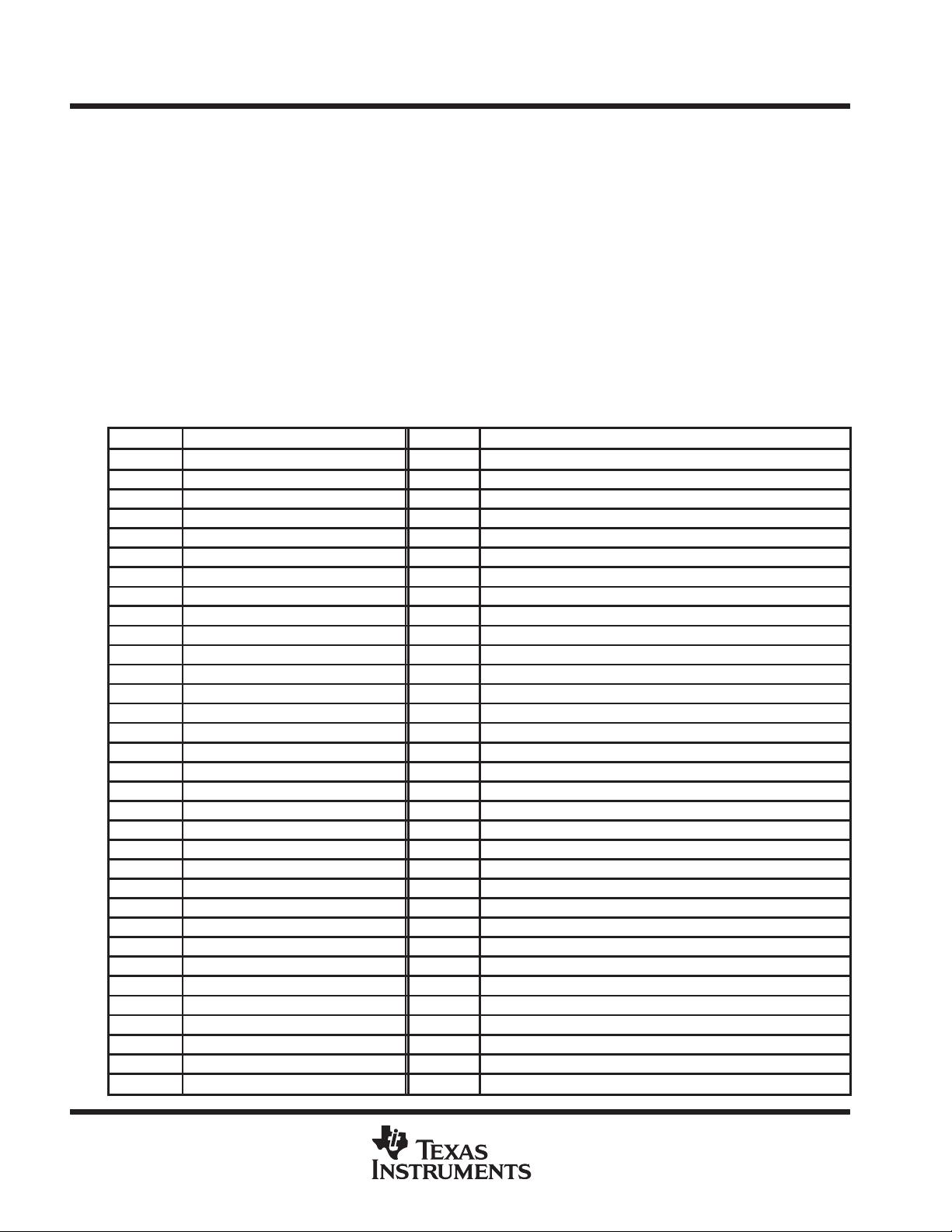

Table 3. Symbols Used in Functional Block Diagram

SYMBOL DESCRIPTION SYMBOL DESCRIPTION

ABU Auto-buffering unit IFR Interrupt-flag register

ACCB Accumulator buffer IMR Interrupt-mask register

ACCH Accumulator high INDX Indirect-addressing-index register

ACCL Accumulator low IR Instruction register

ALU Arithmetic logic unit MCS Microcall stack

ARAU Auxiliary-register arithmetic unit MUX Multiplexer

ARB Auxiliary-register pointer buffer PAER Block-repeat-address end register

ARCR Auxiliary-register compare register PASR Block-repeat-address start register

ARP Auxiliary-register pointer PC Program counter

ARR Address-receive register (ABU) PFC Prefetch counter

AR0–AR7 Auxiliary registers PLU Parallel logic unit

AXR Address-transmit register (ABU) PMST Processor-mode-status register

BKR Receive-buffer-size register (ABU) PRD Timer-period register

BKX Transmit-buffer-size register (ABU) PREG Product register

BMAR Block-move-address register RPTC Repeat-counter register

BRCR Block-repeat-counter register SARAM Single-access RAM

BSP Buffered serial port SFL Left shifter

C Carry bit SFR Right shifter

CBER1 Circular buffer 1 end address SPC Serial-port interface-control register

CBER2 Circular buffer 2 end address ST0,ST1 Status registers

CBSR1 Circular buffer 1 start address TCSR TDM channel-select register

CBSR2 Circular buffer 2 start address TCR Timer-control register

DARAM Dual-access RAM TDM Time-division-multiplexed serial port

DBMR Dynamic bit manipulation register TDXR TDM data transmit register

DP Data memory page pointer TIM Timer-count register

DRR Serial-port data receive register TRAD TDM received-address register

DXR Serial-port data transmit register TRCV TDM data-receive register

GREG Global memory allocation register TREG0 Temporary register for multiplication

HPI Host port interface TREG1 Temporary register for dynamic shift count

HPIAH HPI-address register (high bytes) TREG2 Temporary register used as bit pointer in dynamic-bit test

HPIAL HPI-address register (low bytes) TRTA TDM receive-/transmit-address register

HPICH HPI-control register (high bytes) TSPC TDM serial-port-control register

HPICL HPI-control register (low bytes)