跨时钟域处理:解决FPGA和ASIC设计中的同步挑战

需积分: 22 105 浏览量

更新于2024-09-08

4

收藏 355KB PDF 举报

"这篇文档详细讨论了在FPGA和ASIC设计中常见的跨时钟域处理问题,包括亚稳态、采样丢失等挑战,并提出了六种解决策略。它强调了正确处理这些问题对于确保系统稳定运行的重要性。"

在数字系统设计中,尤其是在FPGA和ASIC应用中,跨时钟域处理是一项至关重要的任务。由于实际系统往往包含多个工作于不同时钟频率的模块,这些模块之间的通信就会涉及跨时钟域问题。不恰当的处理会引入亚稳态、采样丢失等风险,可能导致系统功能失效。

1. 异步设计中的亚稳态

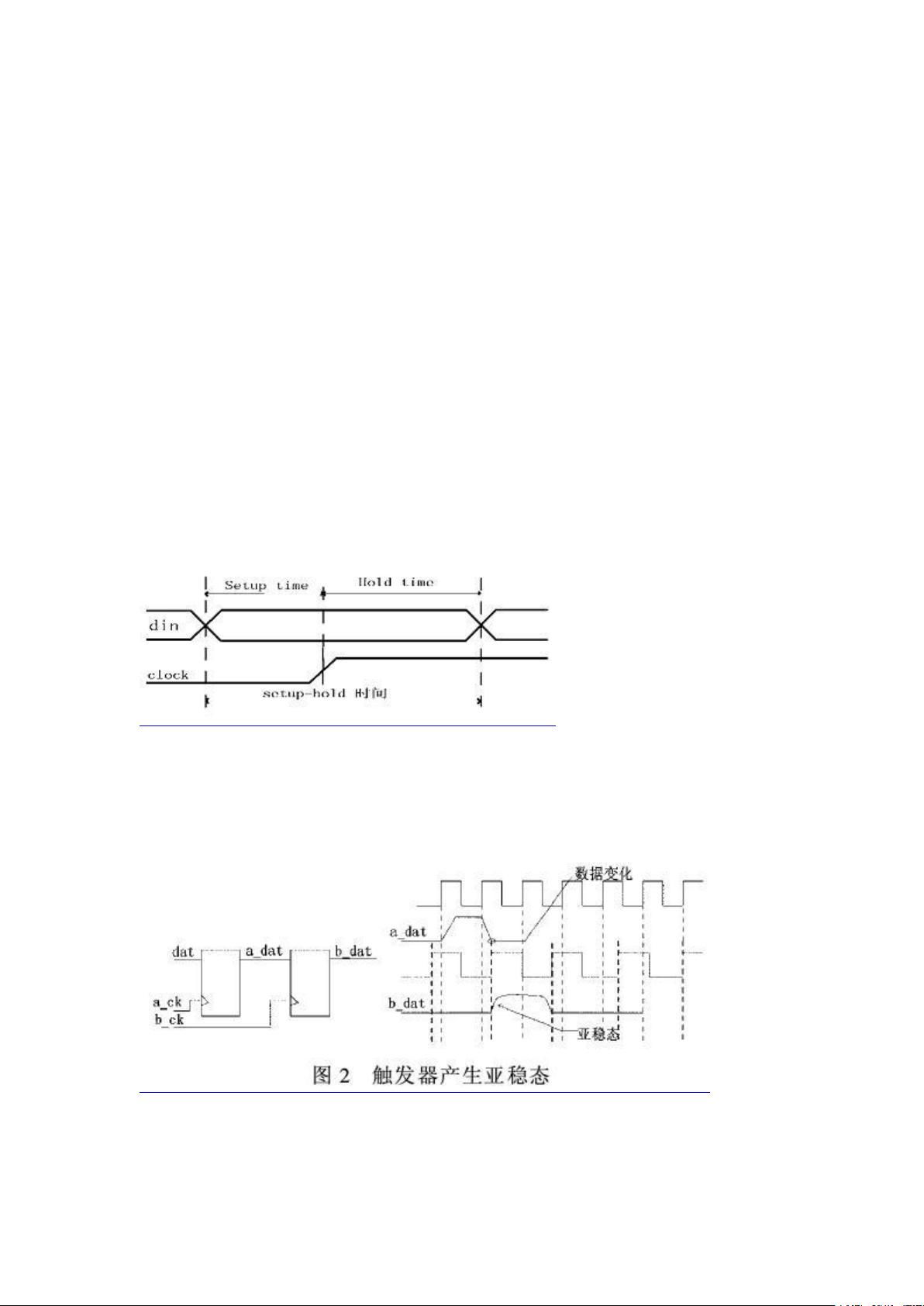

亚稳态是触发器在时钟边沿捕获不稳定输入信号时产生的现象。当输入信号在触发器的建立和保持时间内变化,其输出可能陷入一个不确定状态,既不是0也不是1,而是短暂的中间状态。这种状态的持续时间称为亚稳态时间。亚稳态的存在是跨时钟域设计的主要挑战之一。

2. 亚稳态的影响与解决

如果亚稳态持续时间超过一个时钟周期,它可能会传递到后续的触发器,引发连锁反应,导致整个系统出现逻辑错误。为了评估设计的可靠性,可以计算MTBF(平均无故障时间),它反映了在亚稳态期间系统不受影响的概率。设计的目标是确保MTBF足够大,以降低因亚稳态引起的故障风险。

3. 跨时钟域信号同步方法

文档中提到的六种同步策略可能包括:

- 乒乓缓冲:使用两个触发器在不同时钟域的边缘捕获信号,确保数据稳定。

- 带有DLL(Delay Locked Loop)或PLL(Phase-Locked Loop)的同步:通过锁相技术同步不同时钟域,减少亚稳态发生的概率。

- 数据校验:使用握手协议确保数据在传输前已被正确采样。

- 基于双倍速率的同步:通过提高数据传输速率,使亚稳态窗口减半。

- 滤波器或重试机制:通过多次采样和逻辑判断,滤除亚稳态的影响。

- 无损边沿检测:利用特定的触发器结构,如DFF-with-set-reset或DFF-with-prescaler,避免在不稳定的边沿采样数据。

4. 设计实践

在实际设计中,工程师需要根据系统需求和性能限制选择合适的同步策略。同时,需要充分考虑电源噪声、温度变化等因素,以确保设计在各种条件下都能稳定工作。

跨时钟域处理是FPGA和ASIC设计中的核心问题,涉及到系统稳定性、可靠性和效率。理解和掌握有效的同步策略对于任何数字系统设计者都是必不可少的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-08-14 上传

2011-11-30 上传

2020-07-29 上传

2019-08-09 上传

2019-08-09 上传

wei_qinze

- 粉丝: 0

- 资源: 1

最新资源

- 基于PHP的新浪php问答新春版源码.zip

- C#+SQL2005通讯录管理系统

- React Performance-crx插件

- DataCamp-网络宝座分析

- agile_grasp:ROS软件包,用于检测点云中的抓握姿势

- 程序员最好的网站:程序员有用的一些网站

- blade-component-library:用于为Laravel 7创建可共享刀片组件库的基本模板

- Hack-Tools-crx插件

- 华氏度到摄氏温度

- 会爆炸的苹果flash动画

- 东明文章系统(ASP.NET三层+MSSQL开源版)

- adt-platform:高性能大数据高级分析平台

- Assignment2_iPhone:用CodeSandbox创建

- silentSMS-master

- 基于PHP的欣豚进销存管理系统网络版php版源码.zip

- view-images-bookmarklet:一个书签,用于查找页面上的所有图像并在新窗口中向您显示,以便于查看和下载