Cadence Encounter:数字APR课程详解 - 地址规划与布局

需积分: 15 43 浏览量

更新于2024-07-18

1

收藏 7.52MB PDF 举报

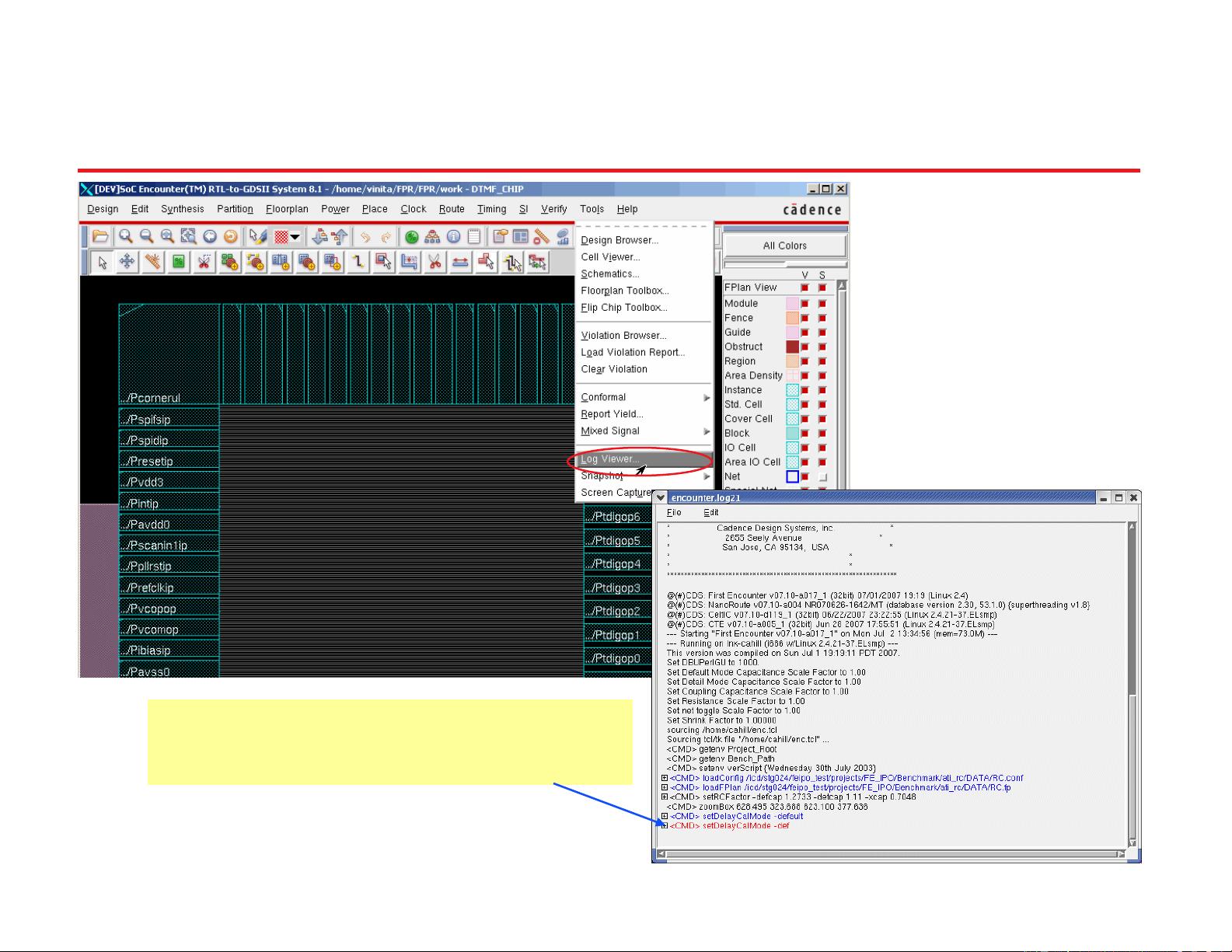

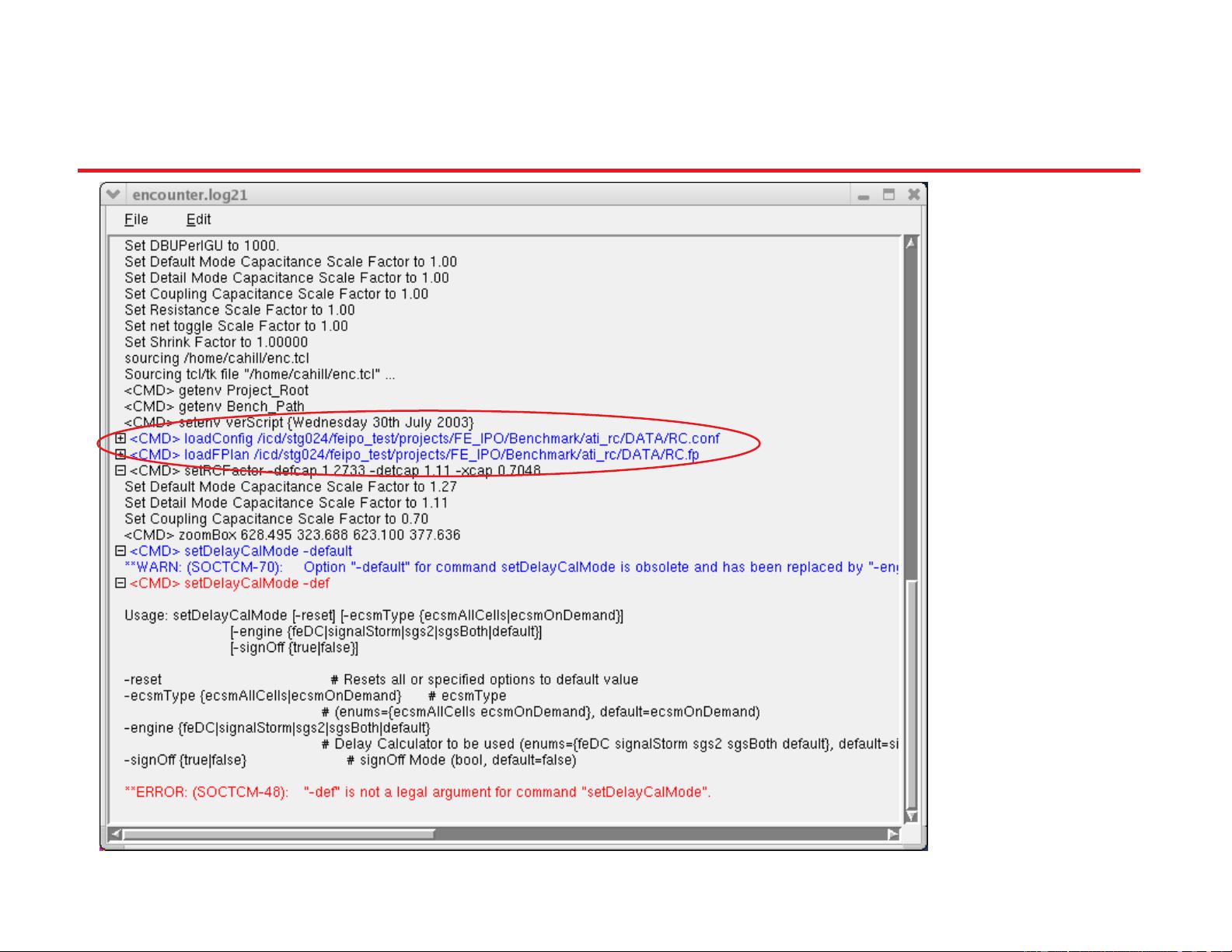

Cadence Encounter是一款广泛应用于数字集成电路设计的综合工具套件,特别在物理布局(Physical Synthesis)、布线(Place and Route)以及 floorplanning 过程中扮演着关键角色。这个课程详细介绍了如何使用Cadence Encounter的8.1版本进行高级设计流程。

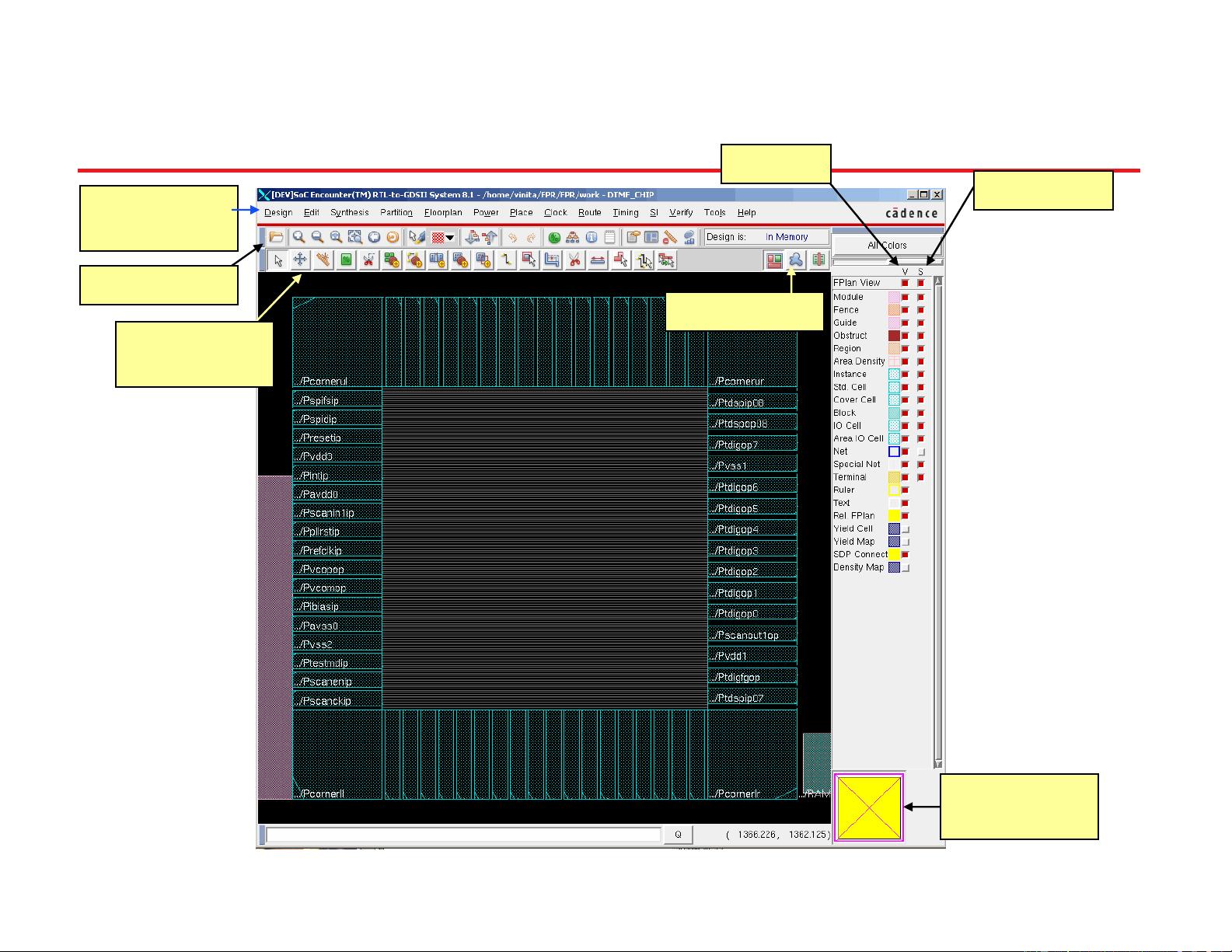

首先,floorplanning是设计过程中的重要环节,它涉及将设计元素(如逻辑门、标准细胞和模块)导入并合理地安排在芯片上,以满足空间效率和信号完整性要求。通过精确的布局,可以优化电路的性能和功耗。

接下来,物理合成(Physical Synthesis)是对逻辑设计进行优化的过程,将原始的逻辑网表转换为物理实现,这包括逻辑优化、布线资源分配等步骤。在这个阶段,工程师会运行功率规划,预测和管理电路的能耗,并通过技术文件(如LEF)来指导优化。

在Place and Route阶段,实际的物理布局开始,包括细节放置(Detailed Placement)操作,即放置标准单元和块,同时进行扫描链重排以减少延迟。此时,工程师会分析路由拥堵情况,确保信号完整性和时序正确性。

提取寄生参数(Parasitic Extraction)是后续步骤,用于生成详细的电路模型,以便进行更精确的时序分析。创建时钟树(Clock Tree Generation)是确保时钟同步的关键步骤,而优化时序(Clock Tree Optimization)则是为了关闭设计中的任何性能瓶颈。

对于关键路径上的信号,可能需要进行屏蔽和间距调整(Routing Critical Nets),以防止干扰和提高信号质量。互动式布线编辑器(Interactive Wire Editor)允许设计师手动调整难以自动处理的部分。

此外,课程还涵盖了解决路由冲突(Routing Violations)、时序和信号完整性问题(Timing and Signal Integrity Violations)的方法,以及实施工程变更单(Engineering Change Order, ECO)的流程。最后,学习者将探索Cadence Encounter的脚本功能(Foundation Scripts),以便在实际设计中灵活应用所学知识。

Cadence Encounter的Digital APR课程提供了一个全面的学习框架,从设计初期的布局规划,到后期的物理实现与优化,确保设计师能够高效地完成高质量的芯片设计工作。通过深入理解并实践这些核心概念和技术,新学习者能够迅速提升其在IC设计领域的专业技能。

2009-11-24 上传

2019-05-23 上传

2013-11-05 上传

2021-04-17 上传

2021-07-06 上传

2023-03-23 上传

2008-12-04 上传

2013-09-10 上传

2011-01-14 上传

空空小二

- 粉丝: 0

- 资源: 5

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载