TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q

10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SLAS052C – MARCH 1992 – REVISED MARCH 1995

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

detailed description (continued)

There are six basic serial-interface timing modes that can be used with the device. These modes are determined

by the speed of I/O CLOCK and the operation of CS

as shown in Table 1. These modes are (1) a fast mode with

a 10-clock transfer and CS

inactive (high) between conversion cycles, (2) a fast mode with a 10-clock transfer

and CS

active (low) continuously, (3) a fast mode with an 11- to 16-clock transfer and CS inactive (high) between

conversion cycles, (4) a fast mode with a 16-bit transfer and CS

active (low) continuously, (5) a slow mode with

an 11- to 16-clock transfer and CS

inactive (high) between conversion cycles, and (6) a slow mode with a

16-clock transfer and CS

active (low) continuously.

The MSB of the previous conversion appears at DATA OUT on the falling edge of CS

in mode 1, mode 3, and

mode 5, on the rising edge of EOC in mode 2 and mode 4, and following the sixteenth clock falling edge in

mode 6. The remaining nine bits are shifted out on the next nine falling edges of I/O CLOCK. Ten bits of data

are transmitted to the host-serial interface through DATA OUT. The number of serial clock pulses used also

depends on the mode of operation, but a minimum of ten clock pulses is required for conversion to begin. On

the tenth clock falling edge, the EOC output goes low and returns to the high logic level when conversion is

complete and the result can be read by the host. Also, on the tenth clock falling edge, the internal logic takes

DATA OUT low to ensure that the remaining bit values are zero if the I/O CLOCK transfer is more than ten clocks

long.

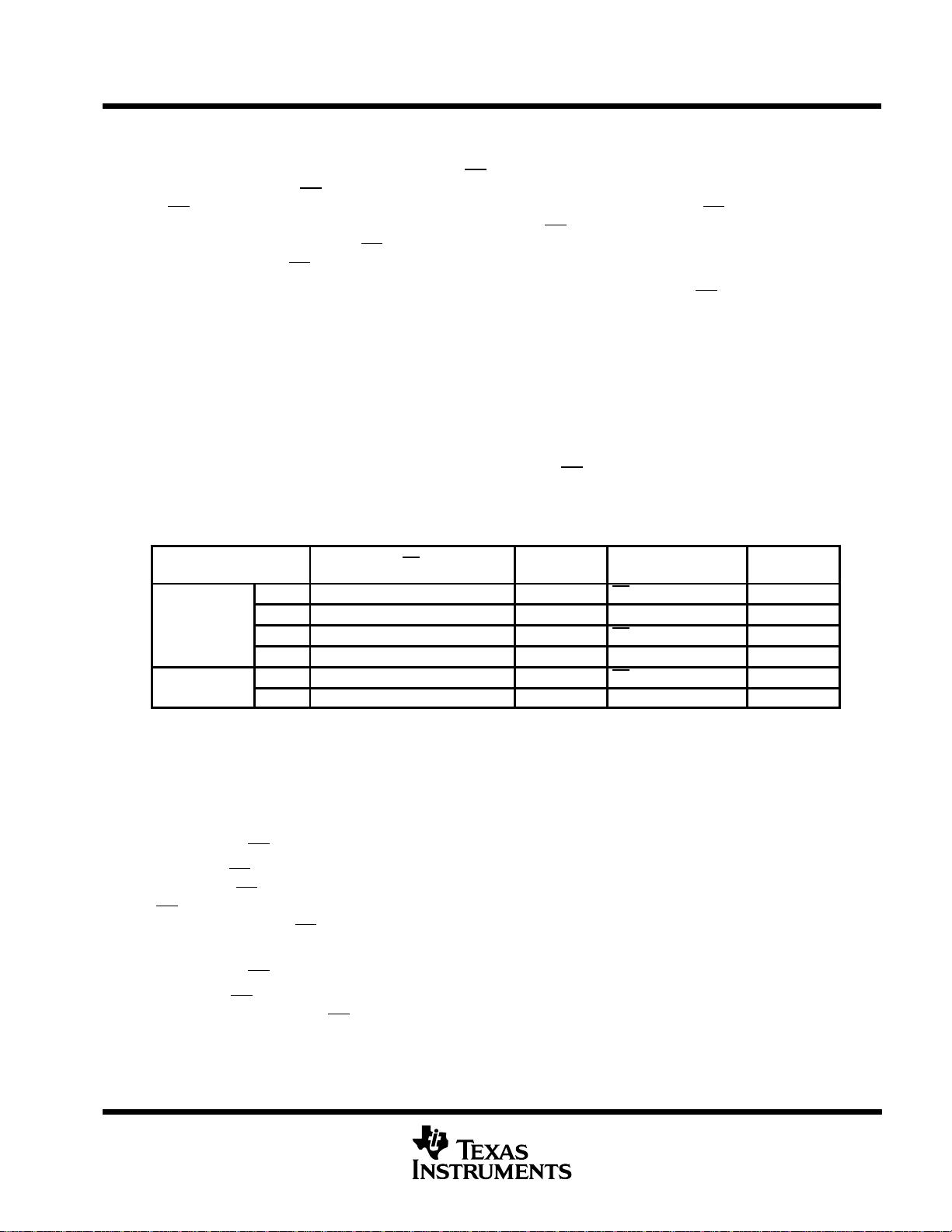

Table 1 lists the operational modes with respect to the state of CS

, the number of I/O serial transfer clocks that

can be used, and the timing edge on which the MSB of the previous conversion appears at the output.

Table 1. Mode Operation

MODES

CS

NO. OF

I/O CLOCKS

MSB AT DATA OUT

†

TIMING

DIAGRAM

Mode 1 High between conversion cycles 10 CS falling edge Figure 9

Mode 2 Low continuously 10 EOC rising edge Figure 10

as

o

es

Mode 3 High between conversion cycles 11 to 16

‡

CS falling edge Figure 11

Mode 4 Low continuously 16

‡

EOC rising edge Figure 12

Mode 5 High between conversion cycles 11 to 16

‡

CS falling edge Figure 13

ow

o

es

Mode 6 Low continuously 16

‡

16th clock falling edge Figure 14

†

These edges also initiate serial-interface communication.

‡

No more than 16 clocks should be used.

fast modes

The device is in a fast mode when the serial I/O CLOCK data transfer is completed before the conversion is

completed. With a 10-clock serial transfer, the device can only run in a fast mode since a conversion does not

begin until the falling edge of the tenth I/O CLOCK.

mode 1: fast mode, CS inactive (high) between conversion cycles, 10-clock transfer

In this mode, CS is inactive (high) between serial I/O CLOCK transfers and each transfer is ten clocks long. The

falling edge of CS

begins the sequence by removing DATA OUT from the high-impedance state. The rising edge

of CS

ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time.

Also, the rising edge of CS

disables the I/O CLOCK and ADDRESS terminals within a setup time plus two falling

edges of the internal system clock.

mode 2: fast mode, CS active (low) continuously, 10-clock transfer

In this mode, CS is active (low) between serial I/O CLOCK transfers and each transfer is ten clocks long. After

the initial conversion cycle, CS

is held active (low) for subsequent conversions; the rising edge of EOC then

begins each sequence by removing DATA OUT from the low logic level, allowing the MSB of the previous

conversion to appear immediately on this output.