SDRAM突发长度解析:内存寻址与工作流程

需积分: 42 58 浏览量

更新于2024-09-09

1

收藏 184KB DOC 举报

"这篇内容主要介绍了SDRAM突发长度的概念,以SDRAM为例,阐述了内存的工作流程和关键参数。"

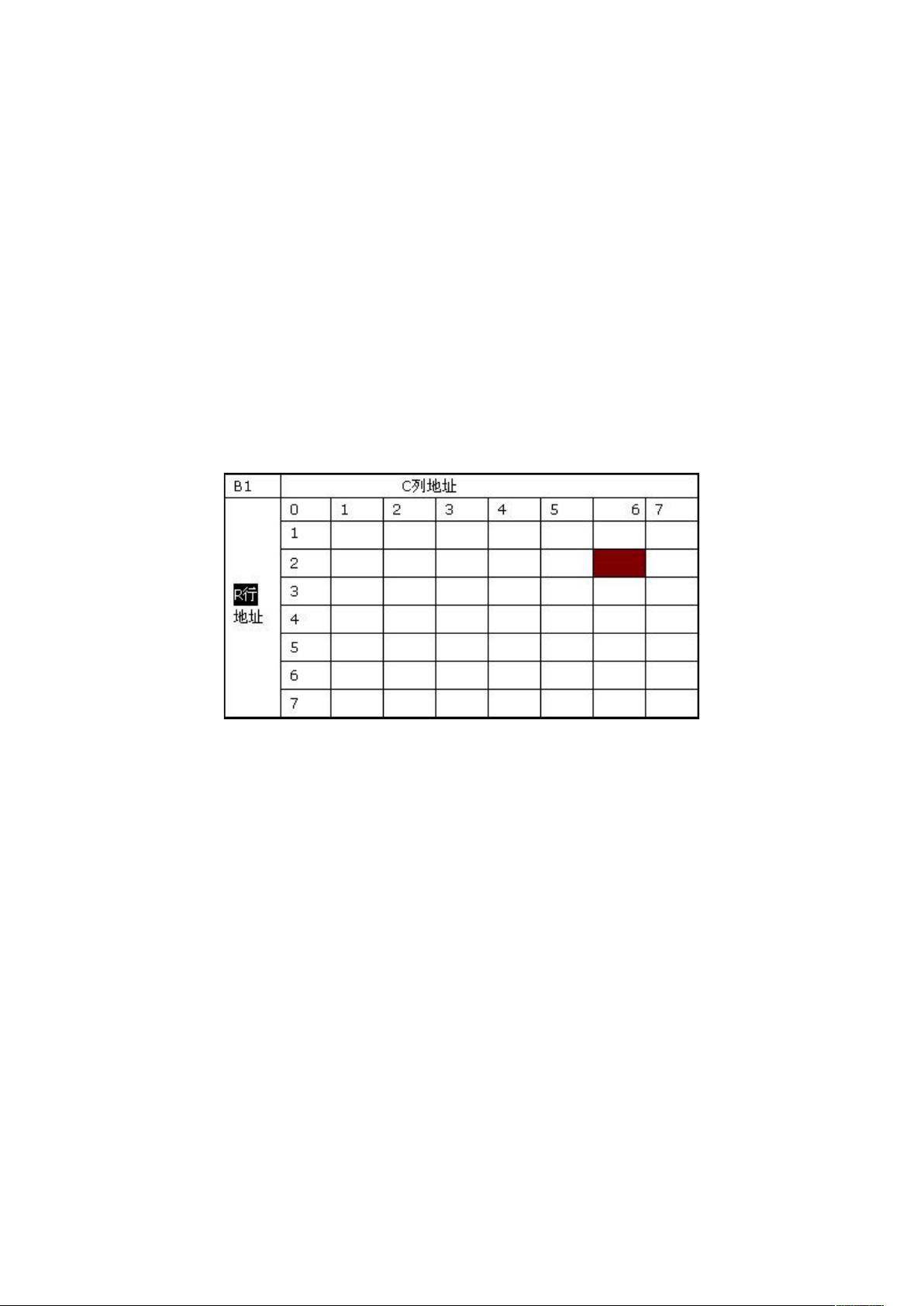

SDRAM(Synchronous Dynamic Random-Access Memory)是一种同步动态随机存取内存,其工作原理基于存储阵列,类似于表格结构。每个存储单元由行地址(Row)和列地址(Column)共同定位。L-Bank(Logical Bank)是内存芯片中的基本存储组织单元,现代内存通常包含4个L-Bank。寻址过程包括:首先选定L-Bank,然后激活行地址,接着指定列地址以完成数据的读写操作。

"行有效"或"行激活"是指同时发出L-Bank和行地址的命令,这个间隔时间称为tRCD(RAS to CAS Delay),表示从行地址选通到列地址选通之间的延迟。tRCD是SDRAM的重要时序参数,可以通过主板BIOS进行调整,以时钟周期数为单位。例如,tRCD=2意味着两个时钟周期的延迟,具体时间取决于内存的时钟频率。

在列地址被选中后,数据传输开始,但数据从存储单元传输到I/O接口还需要一定时间,这个过程涉及另一个关键参数——CL(CAS Latency),即列地址选通延迟。CAS延迟是指从发出列地址选通命令到数据开始出现在内存接口之间所需的时间。

"突发长度"(Burst Length)是SDRAM中的一个重要特性,它定义了一次连续读写操作中传输的数据块大小。例如,如果突发长度为4,那么内存将在一次读写操作中连续访问并传输4个存储单元的数据。这提高了数据传输效率,因为内存控制器可以连续处理一组数据,而不是每次单独访问一个单元,减少了总线的切换次数。

突发模式通常有两种:连续突发(Sequential Burst)和交错突发(Interleaved Burst)。连续突发按照地址顺序依次读取或写入数据,而交错突发则在多个L-Bank间交替进行,以提高内存带宽。

SDRAM的突发长度、tRCD和CAS延迟等参数直接影响着内存的性能和效率。了解这些概念有助于优化系统配置,提升计算机的运行速度。

2019-03-05 上传

2018-07-10 上传

2018-05-03 上传

2023-10-15 上传

2011-07-08 上传

2018-11-29 上传

2010-08-10 上传

2021-10-01 上传

新大陆——

- 粉丝: 11

- 资源: 98

最新资源

- centural_datapack:实时原型制作

- htmlsplit:根据原始标记中的意图,将 HTML 文档拆分为多行

- noise-suppression

- jdbcTemplate-runtime-update:使用Spring Boot在运行时更改DataSources和JdbcTemplate

- GEF-whole-upload,java项目源码,javaoa系统源码下载

- 加登比

- ltsycal0126.zip

- 2.movie-seat-booking

- 科学计算器ZENO-5000

- code_FIV:FIV的后处理

- drabbitmq:QAMQP源码解析,工作量,重新分配,公平分配,订阅发布,主题模式,路由模式,确认机制

- TestStrutsBBS,查看java源码,java校友录网站

- thamilthedal.github.io

- adventofcode2020_googlecolab

- Credit-number-generator:用于生成和验证信用卡号的基本网站

- arduino-moisture:使用 mongo + express 构建的 RESTful API 服务器,用于存储来自我的工厂的数据