VHDL实现的出租车计价器设计与应用

"CPLD/FPGA 出租车计价器的设计"

本设计涉及使用CPLD(复杂可编程逻辑器件)或FPGA(现场可编程门阵列)技术来构建一个出租车计价器,该计价器能够根据行驶里程计算费用,并在3位数码管上动态显示费用和里程。设计的主要目标是实现一个基于VHDL编程的模块化系统,该系统能够准确计费并具备起动、停止和暂停功能。

设计要求如下:

1. **里程计费**:计费规则为起步价6.00元,行驶3公里后每公里收费1.5元。当行驶距离超过10公里时,每公里额外收取50%的费用。车辆暂停或停止时不计费。

2. **显示部分**:采用3位数码管动态扫描电路分别显示车费和里程,每位都能显示一位小数。

3. **操作模拟**:通过开关模拟出租车的起动、停止和暂停状态。起动时,计价器开始计费;停止时,计费停止;暂停时,计费暂时冻结。

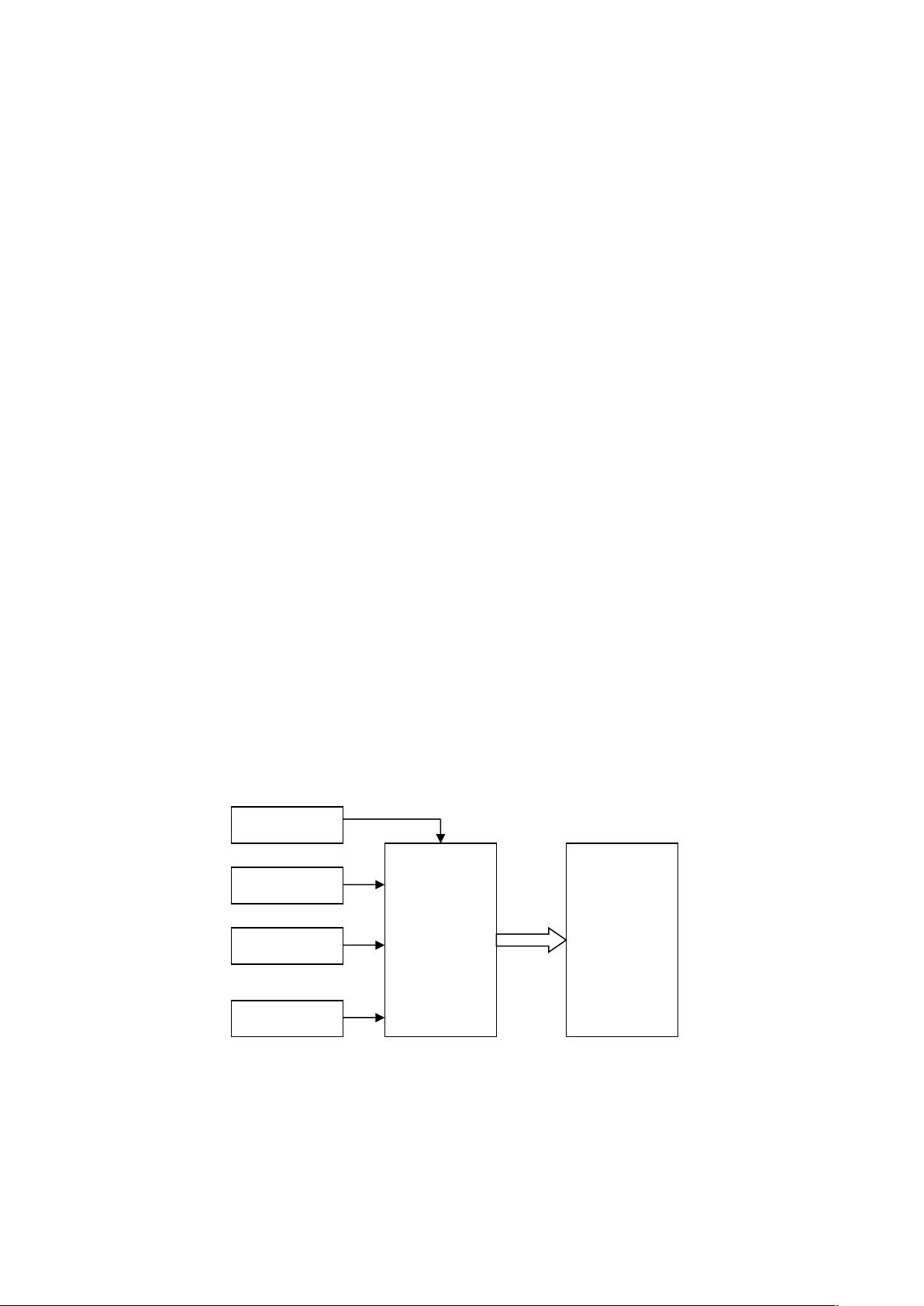

设计中,系统分为控制模块和译码显示模块。控制模块负责计费和里程计数,而译码显示模块则处理费用和里程的显示。

**控制模块**的核心是里程计数和费用计数。计费开始于车辆启动信号,停止或暂停时停止计费。考虑到20MHz的晶振频率,需要将频率分频为1Hz、15Hz和23Hz。1Hz用于里程计数,15Hz和23Hz分别用于不同里程段的费用计数。

**里程计数**通过1Hz脉冲累加实现,当有上升沿脉冲时,从个位开始逐位加“1”,直至满十进位。

**费用计数**则更为复杂,15Hz脉冲在3至10公里区间内对应每公里1.5元的费用,即每增加一公里,费用计数器增加15次。而23Hz脉冲用于10公里以上,每次里程增加时,费用计数器增加的次数等于23,以实现每公里增加50%车费的效果。

**译码显示模块**使用数码管动态扫描技术,确保在3位数码管上正确显示当前的里程和费用,每个数码管均显示一位小数。

总体而言,这个设计项目旨在通过CPLD/FPGA技术实现一个符合实际需求的出租车计价器模型,同时训练学生使用VHDL语言进行硬件描述和模块化设计的能力。通过这样的实践,学生能够深入理解数字逻辑系统的设计和实现过程,以及如何将复杂的计费逻辑转化为硬件描述语言。

175 浏览量

1499 浏览量

225 浏览量

320 浏览量

207 浏览量

1396 浏览量

155 浏览量

1396 浏览量

207 浏览量

michaelfufu

- 粉丝: 0

最新资源

- 小学水墨风学校网站模板设计

- 深入理解线程池的实现原理与应用

- MSP430编程代码集锦:实用例程源码分享

- 绿色大图幻灯商务响应式企业网站开发源码包

- 深入理解CSS与Web标准的专业解决方案

- Qt/C++集成Google拼音输入法演示Demo

- Apache Hive 0.13.1 版本安装包详解

- 百度地图范围标注技术及应用

- 打造个性化的Windows 8锁屏体验

- Atlantis移动应用开发深度解析

- ASP.NET实验教程:源代码详细解析与实践

- 2012年工业观察杂志完整版

- 全国综合缴费营业厅系统11.5:一站式缴费与运营管理解决方案

- JAVA原生实现HTTP请求的简易指南

- 便携PDF浏览器:随时随地快速查看文档

- VTF格式图片编辑工具:深入起源引擎贴图修改