VHDL实战:有限状态机FSM设计与优势解析

需积分: 9 50 浏览量

更新于2024-08-02

收藏 249KB PDF 举报

"VHDL语言实用教程下,是一份关于使用VHDL进行有限状态机FSM设计的教程,适合学习者下载学习。"

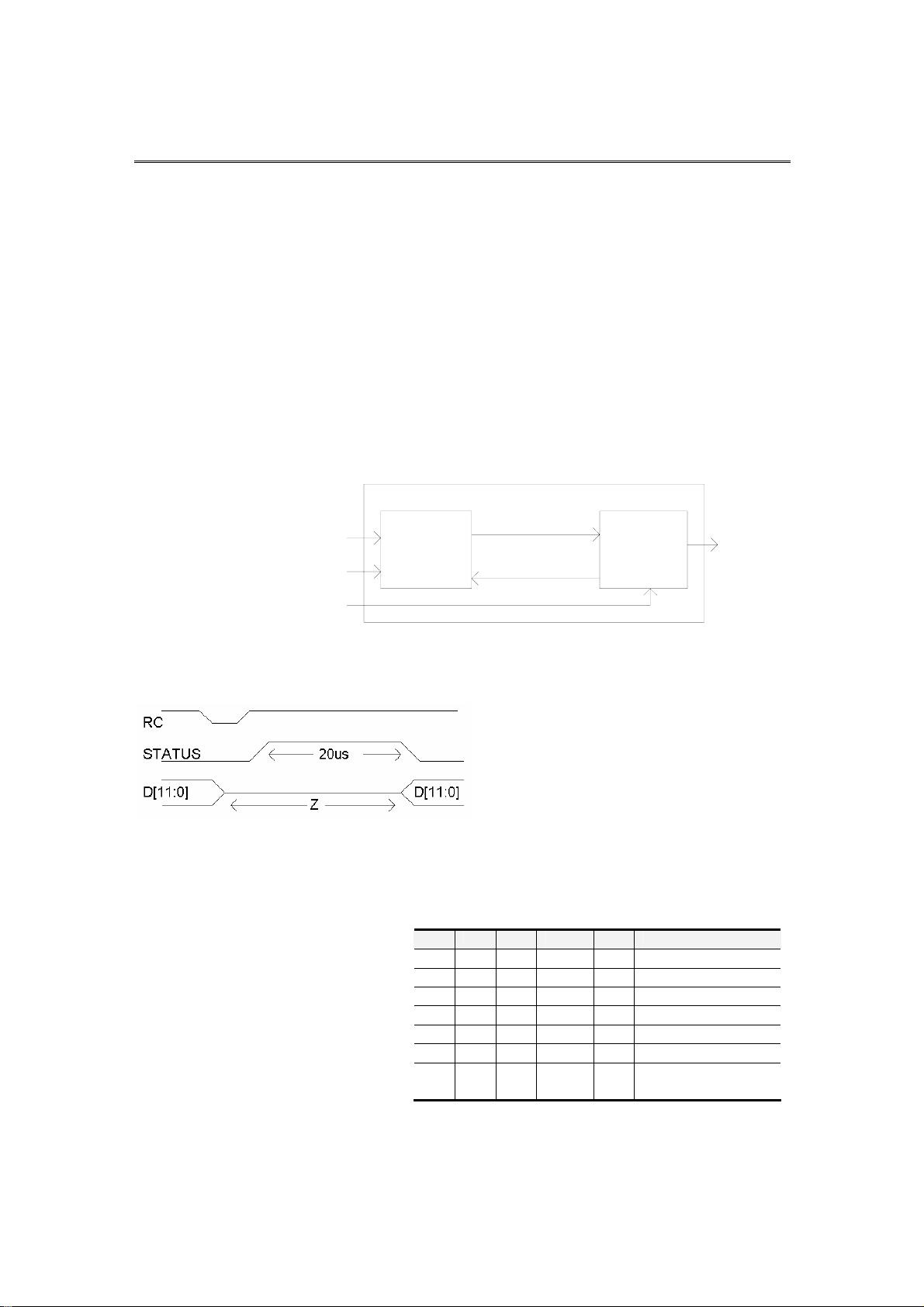

在VHDL语言中,有限状态机(FSM)是一种非常重要的设计工具,尤其在数字系统设计领域。本教程的下部分深入探讨了如何利用VHDL高效地设计和实现状态机。以下是教程中提到的关键知识点:

1. **优化优势**:状态机的结构简单,通常使用枚举类型的定义来描述状态,这种特性使得VHDL综合器能够更好地优化代码,提供高效的硬件实现。

2. **同步时序逻辑**:状态机作为同步时序逻辑模块,能有效地处理竞争冒险现象,这是大规模逻辑电路设计中常见的问题。综合器的优化功能进一步提升了状态机的性能。

3. **设计清晰性**:VHDL中状态机的设计层次分明,结构清晰,易于理解和调试,对于初学者来说,学习和修改状态机设计相对容易。

4. **并行处理能力**:状态机可以由多个进程构成,一个设计实体可以包含多个状态机,这样的并行处理能力使得它们在高速运算和控制任务中表现出色,类似于拥有多个CPU的微处理器。

5. **运行速度**:与CPU相比,虽然两者都是按时钟节拍工作,但状态机的状态转换只需一个时钟周期,而在每个状态中,可以同时执行多个操作。因此,状态机的执行速度通常远超软件系统,特别是在需要快速响应的应用中。

6. **可靠性**:状态机在硬件层面实现,相比于依赖于软件执行的CPU,其结构特点使得状态机在容错性和可靠性方面具有显著优势,更适合于关键任务和高可靠性系统。

7. **应用广泛**:状态机在通信、工业控制和军事等领域有广泛应用,尤其是在需要高效、实时处理的场景下,状态机的设计方案成为了首选。

本教程的下篇可能涵盖了更复杂的状态机设计技巧,如Mealy型和Moore型状态机的对比,状态编码策略,以及如何处理状态之间的转移条件和输出计算。此外,可能还涉及了如何使用VHDL的库和包来增强状态机的功能,以及综合器的特定设置以优化状态机的硬件实现。这些内容对于学习者深入理解和掌握VHDL状态机设计至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-04-03 上传

2009-06-11 上传

2009-06-11 上传

2009-09-01 上传

2008-08-21 上传

2015-01-31 上传

yang0618

- 粉丝: 0

- 资源: 2

最新资源

- 支架附送程序_压力传感器_支架_

- sails-redux:Sails.js和Redux

- day07.zip_界面编程_QT_

- 和尘免费企业网站模板1(绿色风格) asp.net版.zip

- Python库 | roi-device-1.0.12.tar.gz

- 易语言工具提示类模块源码-易语言

- HTML网站源码-设计师品牌介绍网页模板-适配移动端&PC端.zip

- color-api:这是一种REST API,用于获取请求的颜色,其互补色和不同格式的灰度,以及根据其亮度对应于每种颜色的黑色或白色文本

- easyui_Demos_javascript_jqueryeasyui_clothing597_

- flip32plus:Flip32 +原理图

- WhatColorIsIt:http的改编

- 基于HTML5 canvas的仪表盘特效源码 6种.zip

- IME.zip_输入法编程_Visual_C++_

- Python库 | rohdeschwarz-1.8.0.dev1.tar.gz

- 易语言学习进阶结束源码-易语言

- 毕业设计基于J2ee的b2c图书销售系统.zip