数字电路与逻辑设计A卷试题及答案解析

版权申诉

PDF格式 | 353KB |

更新于2024-08-24

| 149 浏览量 | 举报

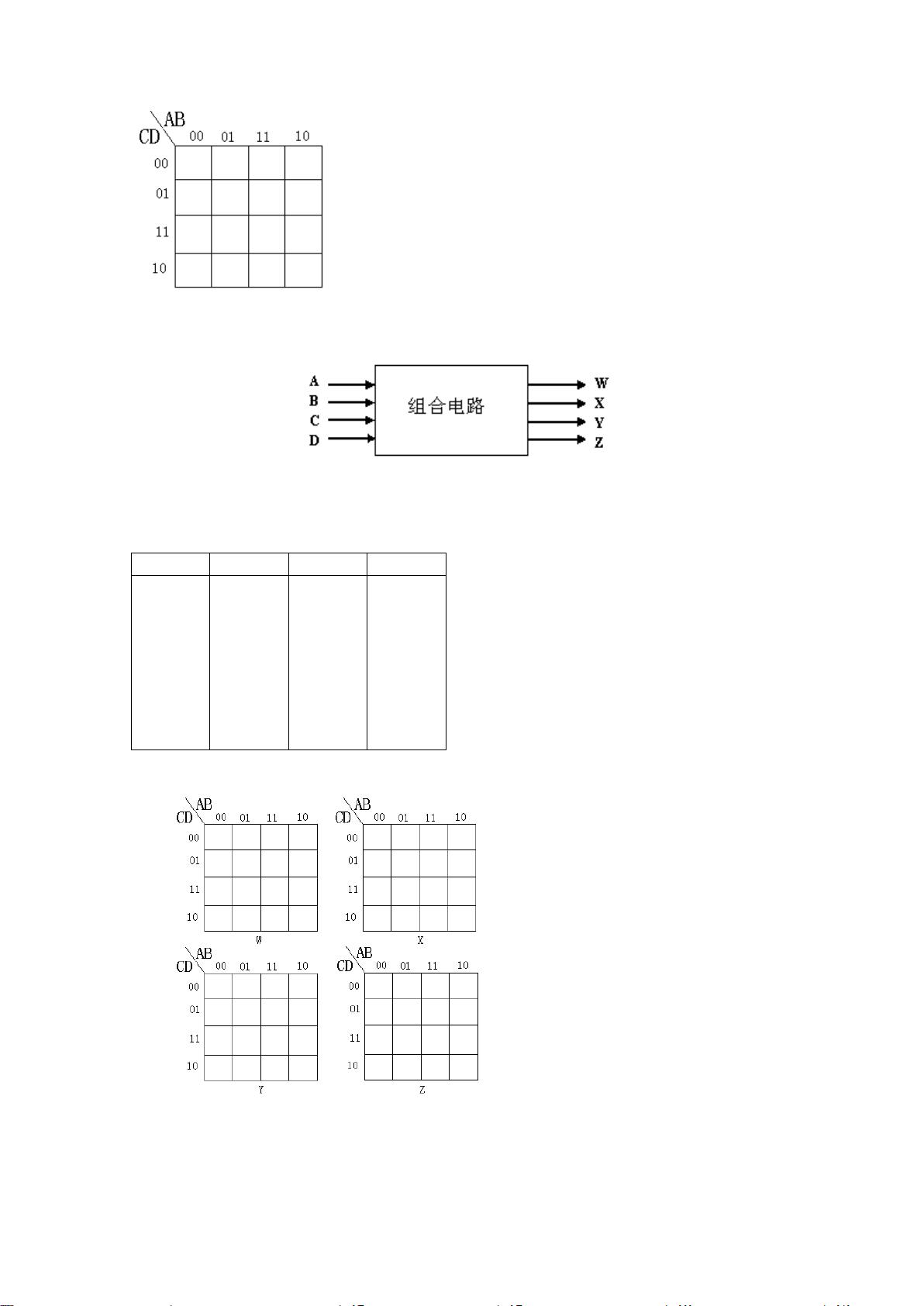

"该资源为《数字电路与逻辑设计(A 卷)带答案》的PDF文件,适用于期末考试复习,包含数字电路相关的单选、判断和多选题,涉及二进制、编码、逻辑门、触发器等内容。"

本文将详细解释与数字电路和逻辑设计相关的一些核心知识点。

1. **二进制数表示**:题目提到表示任意两位无符号十进制数需要的二进制数,这涉及到二进制和十进制之间的转换。任意两位无符号十进制数的最大值是9(1001),因此至少需要4位二进制数来表示,选项C(8)是正确的。

2. **编码系统**:余3码和2421码是两种不同的编码方式,转换需要了解这两种编码的规则。例如,余3码是一种带有借位的二进制编码,而2421码是一种不带借位的BCD码,具体的转换需根据编码规则进行计算。

3. **补码表示**:补码用于表示有符号二进制数,题目中给出的补码1.1000表示的是负数,真值计算需要取反加1,所以选项B(-1.0111)是正确的。

4. **逻辑表达式**:标准或-与式是由最小项相或组成的,因此选项B是正确的。

5. **逻辑函数反演**:反演规则是逻辑函数的一种转换,题目中给出的函数经过反演后,需要找到与之相对的逻辑表达式,具体计算涉及德摩根定律。根据反演规则,正确答案是D。

6. **逻辑门功能**:与门、或门、非门是基本的逻辑门,而与非门可以通过组合实现基本逻辑运算(与、或、非)。因此,选项D是正确的。

7. **触发器转换**:D触发器改造成T触发器通常需要通过附加门电路实现,其中D触发器的非门输出和输入D之间需要一个异或门,故选项C是正确的。

8. **乘法电路**:两个四位二进制数相乘的组合电路会产生16个乘积项,加上一个进位标志,所以输出函数应有17个,但题目中只给了四个选项,可能是题目设计的局限,所以根据选项,选择C(10)可能是要求的输出数量。

9. **JK触发器**:当JK触发器的JK输入为11时,其时钟作用下的次态会反转,即Q' = Q。

10. **奇偶校验码**:奇偶位发生器用于检测二进制数据的错误,采用偶校验码意味着数据位和校验位的1的个数必须是偶数。设计一个四位的奇偶位发生器,需要对所有可能的四位二进制数进行异或,产生一个奇偶位,因此需要4个异或门。

**判断题解析**:

1. 正确。原码和补码都可以通过加法来实现加法和减法运算的转换。

2. 错误。逻辑函数的描述有误,应为m(0,2,5)和M(1,3,4,6)分别对应最大项和最小项的互补关系。

3. 正确。简化状态表时,最大等效类的数量就是最简状态表中的状态数。

4. 正确。并行加法器的先行进位可以显著减少加法运算的时间延迟。

5. 未提供题目图像,无法判断,但一般情况下,带有反馈回路的电路可能涉及同步和异步的概念。

**多项选择题**:

由于题目没有提供具体选项,这部分无法给出详细解答,但通常这类问题需要考生对逻辑门的性质、逻辑表达式的简化、触发器的工作原理等有深入理解。

总结,这个资源涵盖了数字电路和逻辑设计的基础知识,包括二进制编码、逻辑函数、触发器、错误检测、组合电路和时序电路的设计等,适合于期末考试复习。学习者应该掌握这些基本概念和计算方法,以便理解和解决问题。

相关推荐

我慢慢地也过来了

- 粉丝: 1w+

最新资源

- PowerBuilder8操作指南:精确函数与实用示例

- CSS布局与Web标准实战解析

- C#类型转换深度解析:装箱、拆箱与转换技巧

- MIDP 2.0 游戏API实战指南

- 《软件测试艺术》第二版——探索软件测试的精髓

- 新版C#设计模式手册:全面解读23种设计模式

- 英汉对照:人力资源管理常用术语解析

- ASP.NET Form认证详解及单点登录实现

- C#经典教程(下):从语言概述到面向对象设计

- C#入门到精通教程

- 《深入浅出MFC》2/e电子书免费下载

- 《深入浅出MFC》2/e电子书免费下载

- 《深入浅出MFC》2/e电子书免费下载

- 《深入浅出MFC》2/e电子书免费下载

- 《深入浅出MFC》2/e电子书免费下载

- 《目标》:简单常识解决复杂管理的艺术