基于FPGA的RISC CPU设计:从入门到实践

需积分: 50 178 浏览量

更新于2024-07-17

收藏 2.63MB DOC 举报

本文档是一份关于基于FPGA的最简RISC CPU设计的详细课程报告,撰写于2017年3月26日。该设计旨在帮助学习者深入理解计算机处理器的基本结构,特别是RISC(精简指令集计算机)架构。CPU设计主要包括以下几个关键部分:

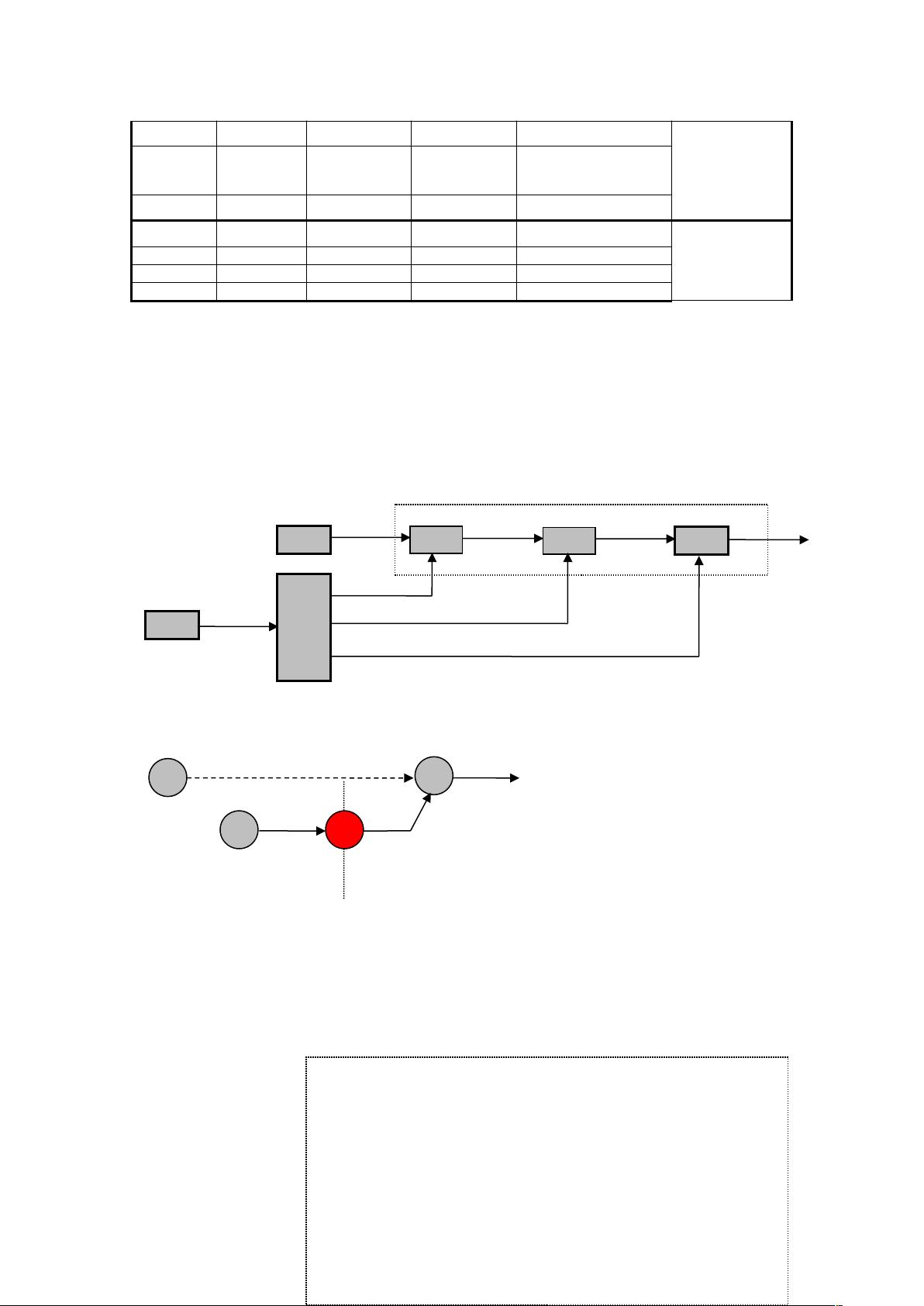

1. SPM_CPU设计:设计的核心是创建一个简单但功能齐全的处理器,具有4个8比特寄存器,用于指令和数据存储。它采用了Ciletti的指令设计方法,具体指令如NOP(无操作),ADD(加法),SUB(减法),AND(逻辑与)等,每个指令都有明确的操作码、源操作数和目标操作数,以及数据地址。

- 取指周期:设计中详细描述了CPU的控制器如何执行取指操作,确保指令的连续执行。

- 运算指令:包括ADD、SUB、AND等,展示了它们的执行过程和对寄存器的操作。

- 跳转指令(BR)、零标志转移(BRZ)以及读写指令(RD、WR)等控制流程,使得程序能按预期执行。

- 停机指令(HALT)和输出指令(OUT)用于程序终止和数据输出,增加了系统的实用性。

- 提供了两个测试程序,分别是流水灯和斐波那契数列,分别展示了CPU如何处理不同类型的数据和算法。

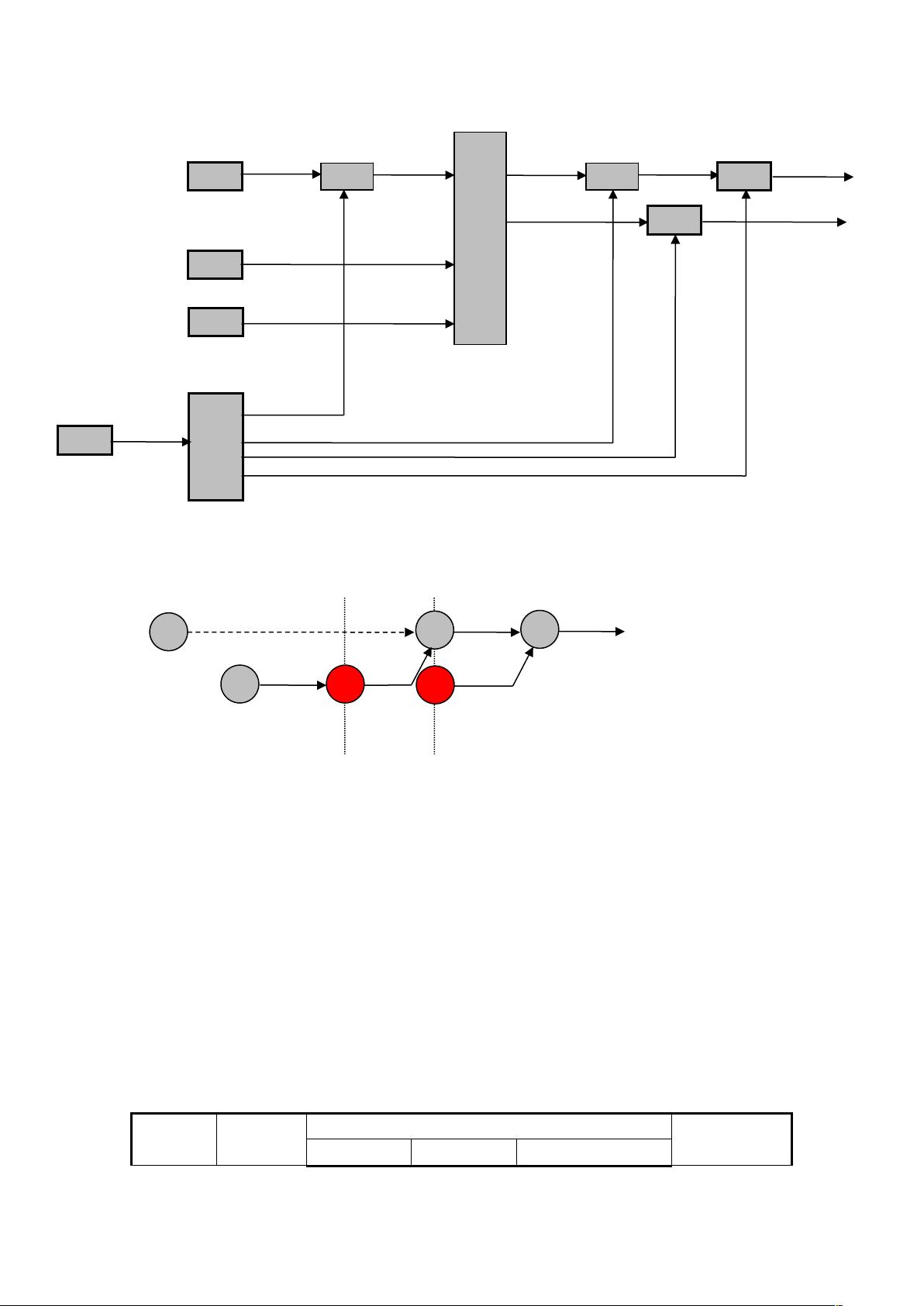

2. RISC_CPU设计:这部分进一步深化了CPU的设计,包括顶层架构设计,片上系统(SoC)的构建,以及地址映射表的实现。指令系统设计详细阐述了指令格式和指令码表,强调了不同指令的执行效率。

- 指令节拍分析:着重于分析每条指令的执行时间,包括取指周期、运算指令执行、数据读写操作等,这有助于优化CPU性能。

- 中断处理:设计中包含了无条件转移指令、零标志转移指令(SKZ)和中断返回指令,以支持中断处理机制。

- 片内外数据指令区别:区分了CPU内部和外部数据的访问,体现了处理器对内存管理的考虑。

这份报告不仅涵盖了CPU的基本组成部分和工作原理,还通过实例演示了如何将理论知识应用于实际设计中,适合作为学习者理解CPU内部结构和实现的基础教程。通过完成这个项目,学生能够加深对计算机体系结构的理解,提高硬件编程和调试能力。

2012-10-28 上传

2021-03-16 上传

2022-06-25 上传

2022-06-26 上传

2021-10-06 上传

2023-06-20 上传

2021-09-07 上传

2023-06-20 上传

bigbird2444

- 粉丝: 0

- 资源: 4

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍